前回のblogでは、サンプルのプログラムを動かして、テストパターンを表示した。今回は、オリジナルの画面をultra96のDisplay Portに表示しようと思う。

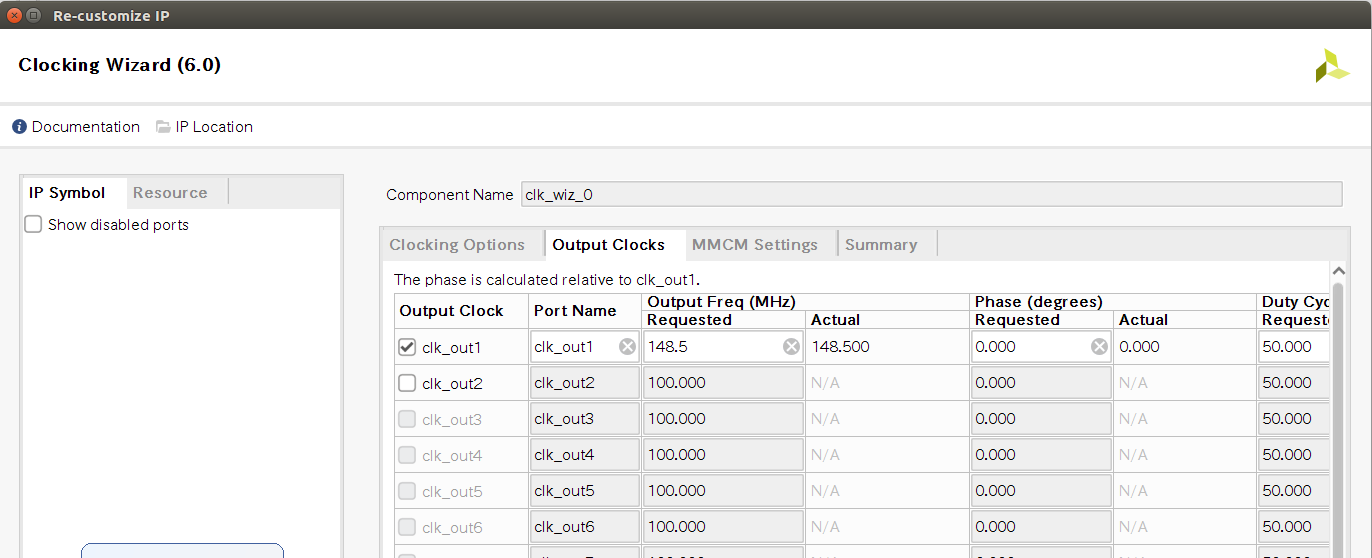

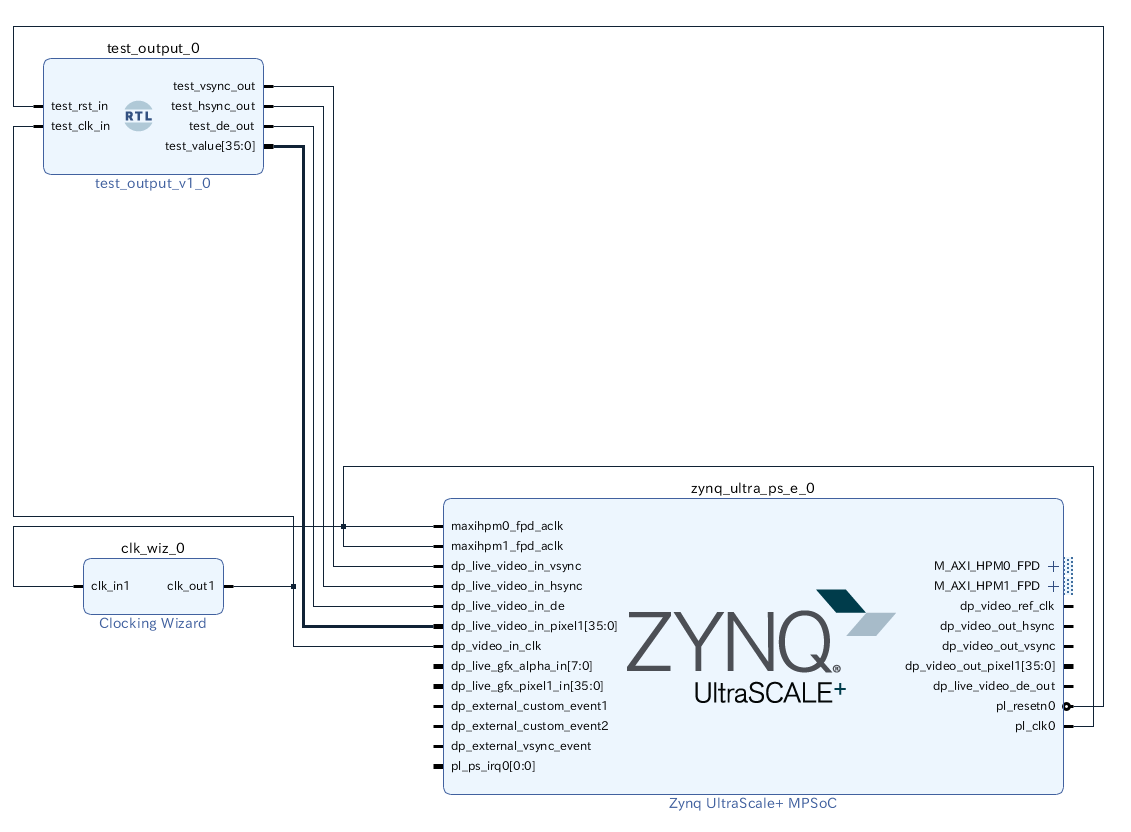

IPカタログからclk_wizを選択してクロックを用意する。今回は、1920×1080 60Hzをターゲットとしたので、クロックは、148.5MHzを出力する。

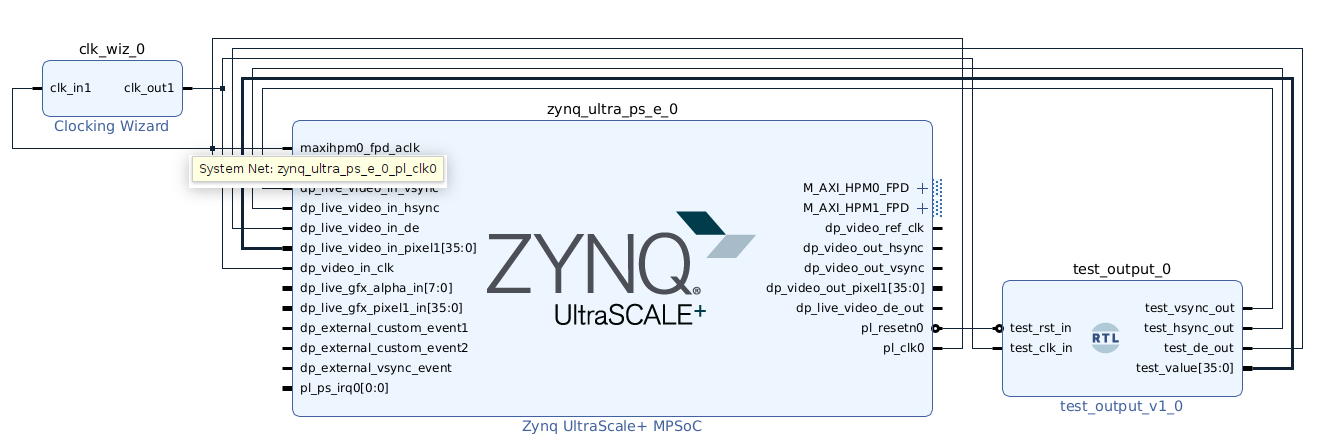

そして、もう1個、任意の画像を出力するモジュールを自作した。test_outputになる。こちらは、clk_wizから入力した148.5MHzから、V、Hとeneable信号を生成し、表示する画像も生成するモジュールになる。

最後に、ZYNQのPSに、Display Portを有効にして、LIVE_SOURCEとして入力すれば良い。

以下、画面が表示された時の写真になります。見えないけど、外枠の画素は、上が緑、左が赤、右が水色、下がブルーになっている。

一応、モニターの表記に、1920×1080 H 67kHz, V60Hzとなっているので、受信できている。

(PCの出力と同じ表記になった。)

以下に、これらのプロジェクトファイルをおいてあります。

https://github.com/y38y38/fpga/tree/master/d5/

では、簡単に説明させて頂きたいと思います。

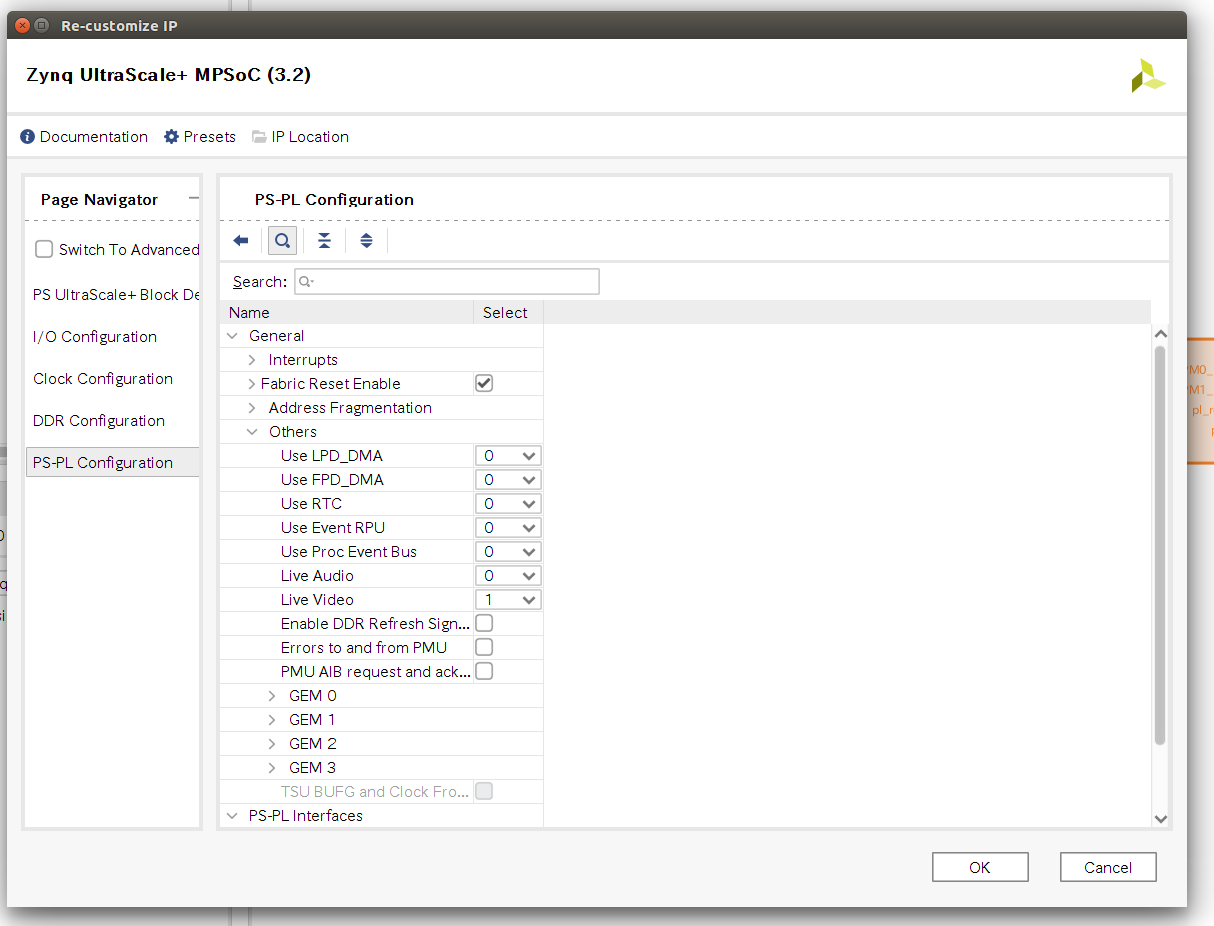

最初に、Open Block Diagramで、BLOCK DESIGNを開き、ZYNQを追加する。そして、Auto Settingをして、次にZYNQをクリックしてカスタマイズする。PS−PL Configuration→General→Others→Live Videoを1にする。これでPLからの入力をdiplay portに出力するはずだ。

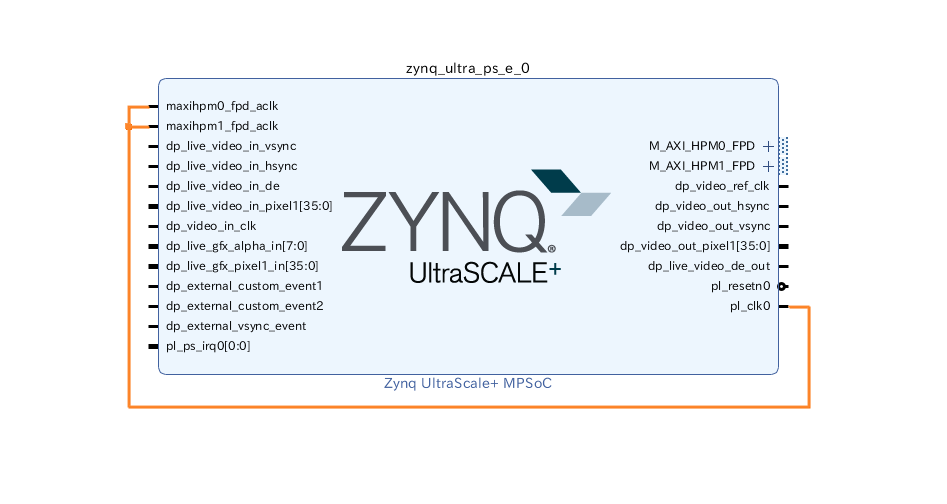

そして、pl_clk0をmaxihpm0_fpd_aclkとmaxihpm1_fpd_aclkに接続する。

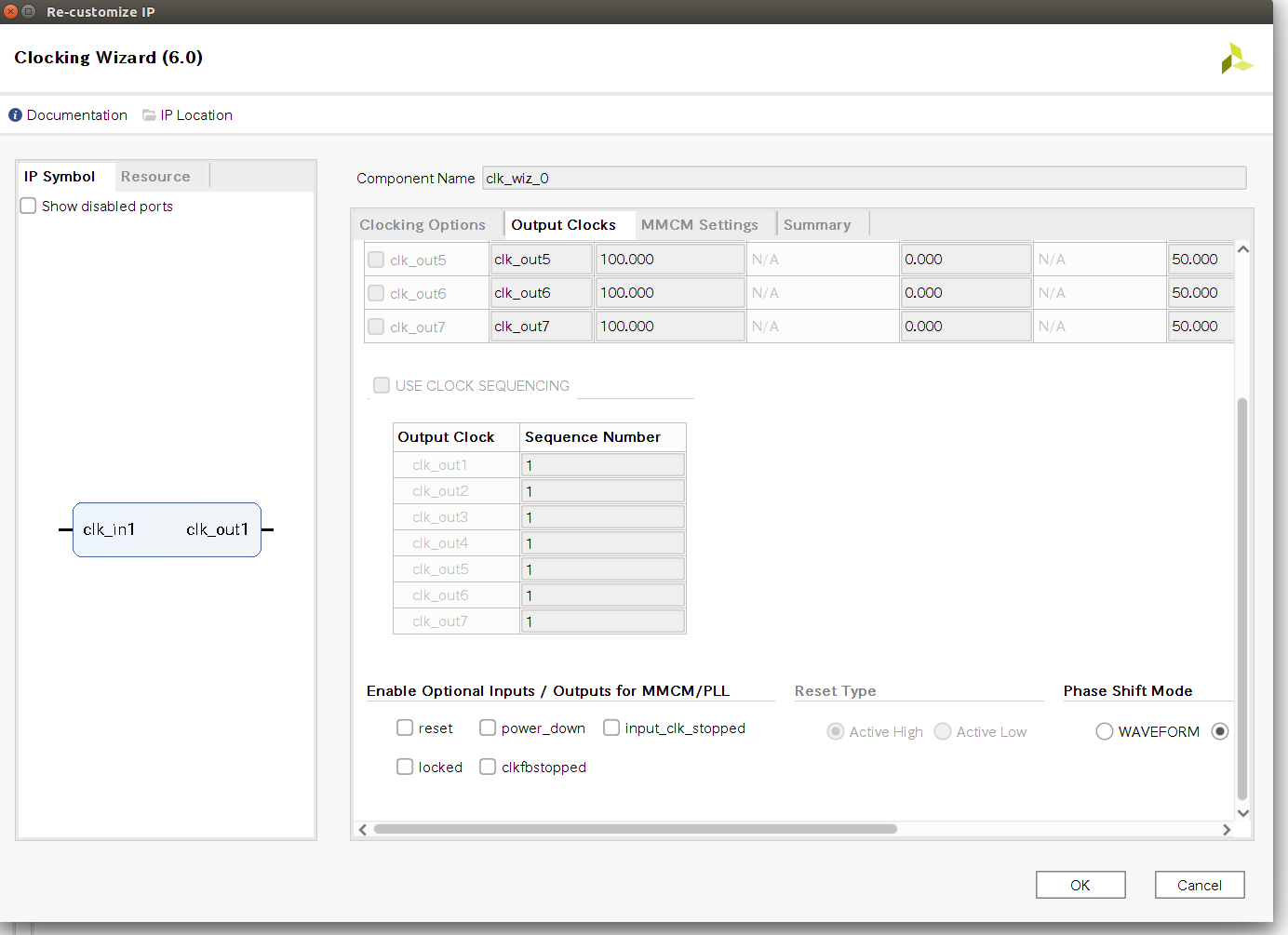

次に、+ボタンをクリックして、clk_wで検索して、clocking Wizardを選択して追加する。最初は不安定でも良いと思ったので、Enable Optional の箇所でチェックを外して、resetとlockedの端子は削除した。

で出力するClockですが、148.5MHzにする。

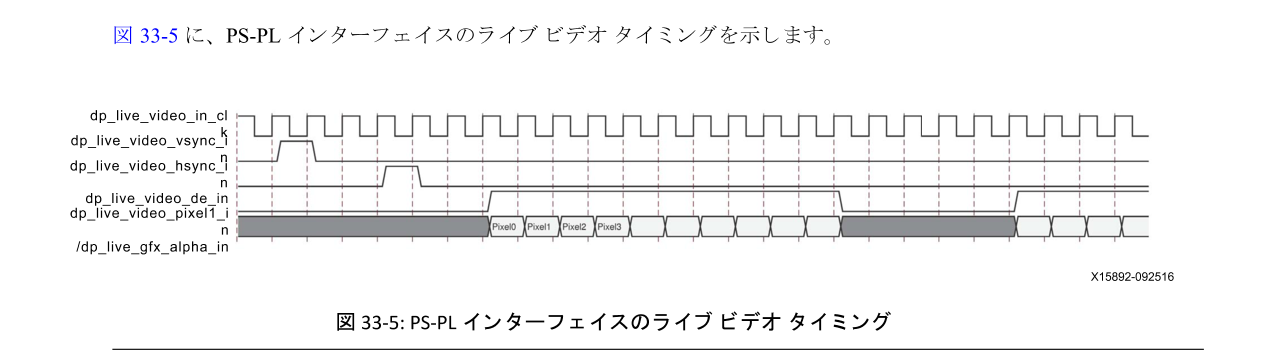

では、この148.5MHzの値ですが、まずは、ZYNQのdisplay PortにLIVEで入力しなければいけない値が5つある。

・dp_video_in_clk

・dp_live_video_in_vsync

・dp_live_video_in_hsync

・dp_live_video_in_de

・dp_live_video_in_pixel1[35:0]

これらの説明は、テクニカルリファレンスマニュアルに乗っている。しかし、結構よくわらなく、図としては以下が載っている。

これをみるとvsyncとhsyncはある1クロックの間にHighになって、あとは、有効なデータがある時に、deを出力すればよさそうだ。でもvsyncとhsyncをHighにするタイミングと、deの関係がわからなかった。

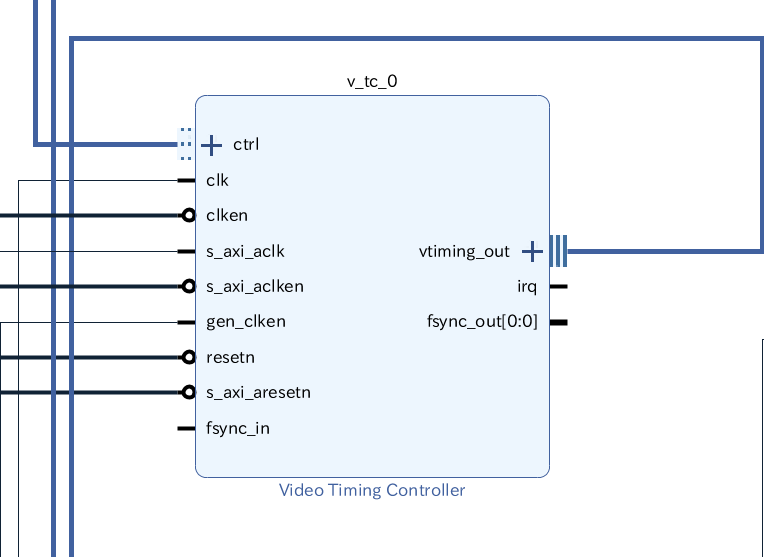

vsyncとhsyncは、Adamさんのプロジェクトを参考にした。Adamさんのプロジェクトでは、hsyncとvsyncは、Video TIming ontrollerというモジュールを使用して生成しているようだ。以下は、Adamさんのプロジェクトの画像だ。

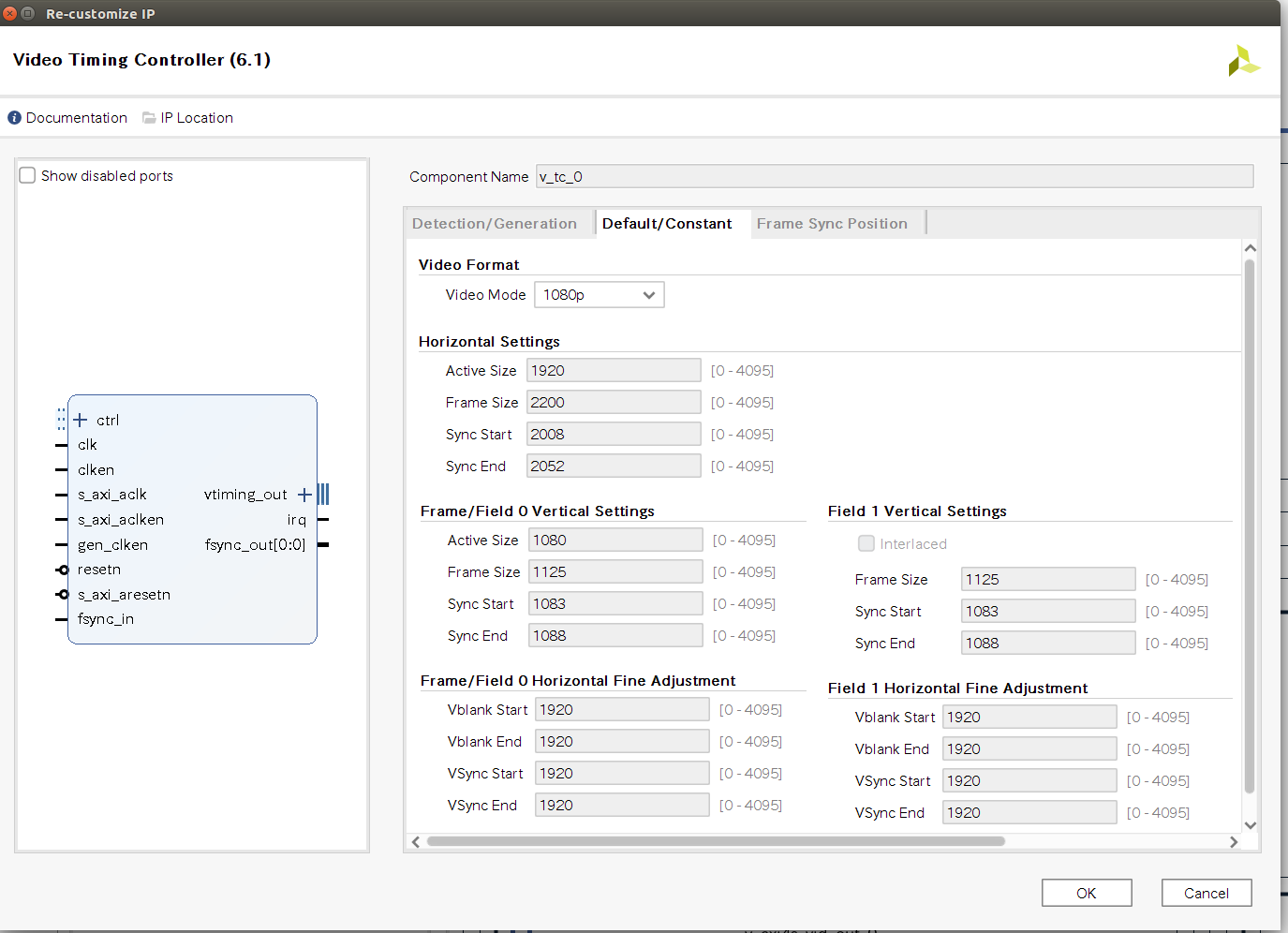

Adamさんのプロジェクトは、1280×720のサイズの出力をしている。そこで、Video Timing Controllerをクリックして、Default/Constantを表示させる。そして、Video Modeを1080pとする。そうすると以下の画面が表示される。

今回は、これを真似する。

Sync Start〜Sync Endの箇所をhsyncとvsyncでHighにすることにした。

また、deは、よくわからなかったので、H方向は、0〜1919。V方向は0〜1079の間にHighにすることにした。

そこで、148.5MHzの算出方法ですが、このVideo Timing ControllerのFrame Sizeを見ると、1920×1080に対して、2200×1125のサイズで送出されるようになっている。よって60Hzなので、

2200x1125x60 = 148500000になる。よって、Clockは148MHz用意するばよさそう。

で、次に、148.5MHzのクロックを入力して、hsync,vsync、deを生成して、画像を出力するモジュールを準備する。diplay Portに出力する画像は、全体が白で、一番外枠だけ、色をつけてみました。

全体が0だと黒で、1だと白になる。黒だと入力されているか不明なので、白にすることにした。このモジュールはgithubにあるのでそちらを参照してほしい。

そして、モジュールを追加したら各信号を接続しておく。

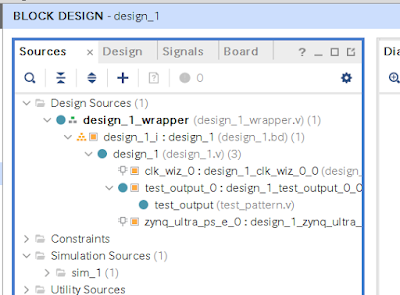

そして、BLOCK DESIGN→Sourcesで、design_1_で右クリックCreate HDL Wrapperして、design_1_wrapperでSet as Topをしておく。

そしてたら、Generate BitStreamをして、bistreamを生成する。完成したら、include bitstreamをチェックして、Export Hardwareする。

次にソフトウェアの準備だ。ZYNQの辛いところは、FPGAだけでなくソフトウェアも準備しないと行けないところだ。

ソフトは、前回の記事と同じ方法で用意するが、

追加したサンプルのxdpdma_video_example.cのInitDpDmaSubsystem()の以下の部分を修正する。

修正前

—————————

XAVBuf_InputVideoSelect(AVBufPtr, XAVBUF_VIDSTREAM1_NONE,

XAVBUF_VIDSTREAM2_NONLIVE_GFX);

修正後

—————————

XAVBUF_VIDSTREAM2_NONE);

—————————

それでビルドしたら、sdkよりprogram bitstreamで、JTAGでbistremaを流し、xdpdma_video_sampleを実行すればOKです!!

本当は、VESAの規格書とか読んでしっかり信号つくる必要あるのかもしれませんが、一応、これで表示ができました!!!!