ultra96のbitstreamを作るために、Board Fileを用意する

のサイトに行き、gitのアドレスをコピペする

PCで、適当な場所で、

git clone https://github.com/Avnet/bdf.gitと実行する。そして、ダウンロードしてきたファイルをインストールしたVivadoにコピーする

cp -r ./bdf/* /tools/Xilinx/Vivado/2020.2/data/boards/board_files/Vivadoを起動するために、スクリプトを実行する。インストールしたディレクトリにsettings64.shがあるはずだ。

source /tools/Xilin/Vivado/2020.2/settings64.shそして、vivadoを起動する

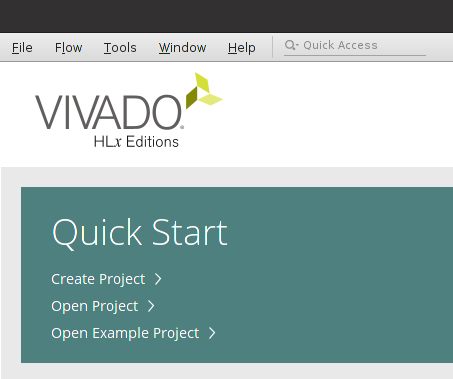

vivadoQuick StartのCreate Projectをクリックする

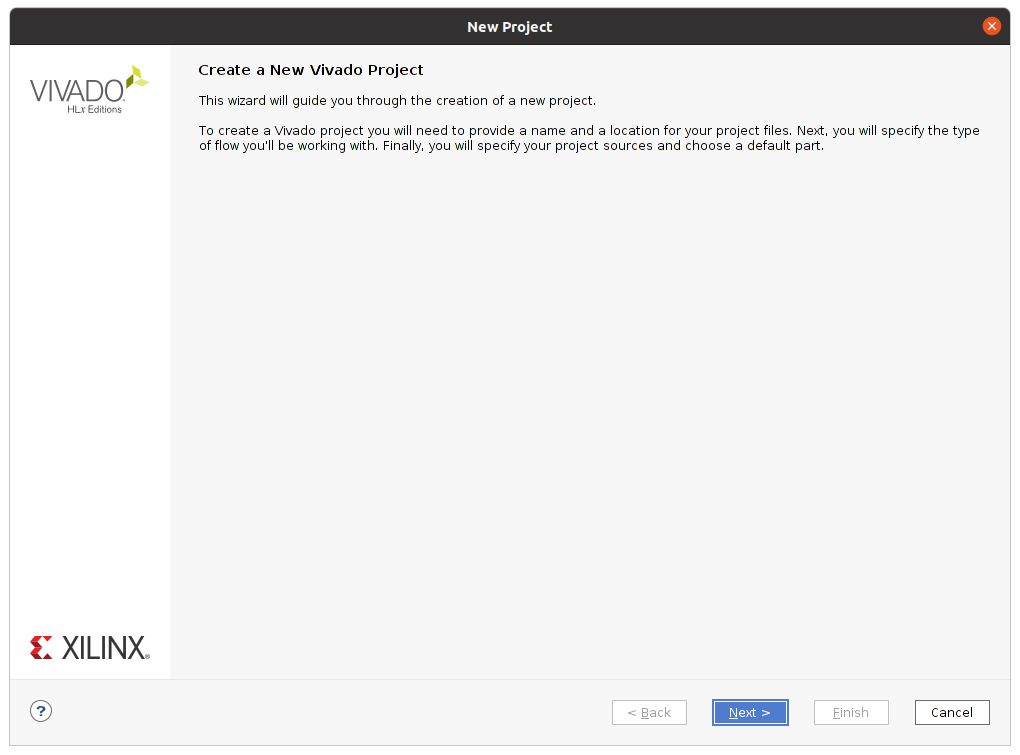

New Projectで、Nextをクリックする

New Projectで、ディレクトリとProject名を適当に設定して、Nextをクリックする

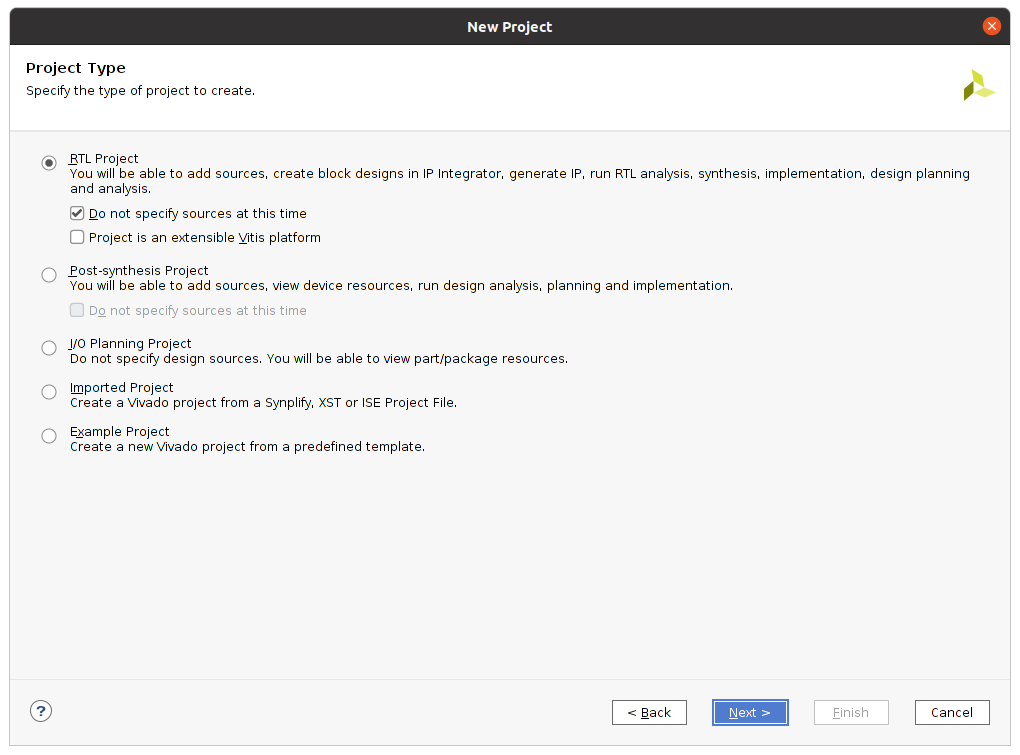

今回は特に何も実装しないので、Do not specify sources at this timeにチェックを入れて、Nextをクリックする。

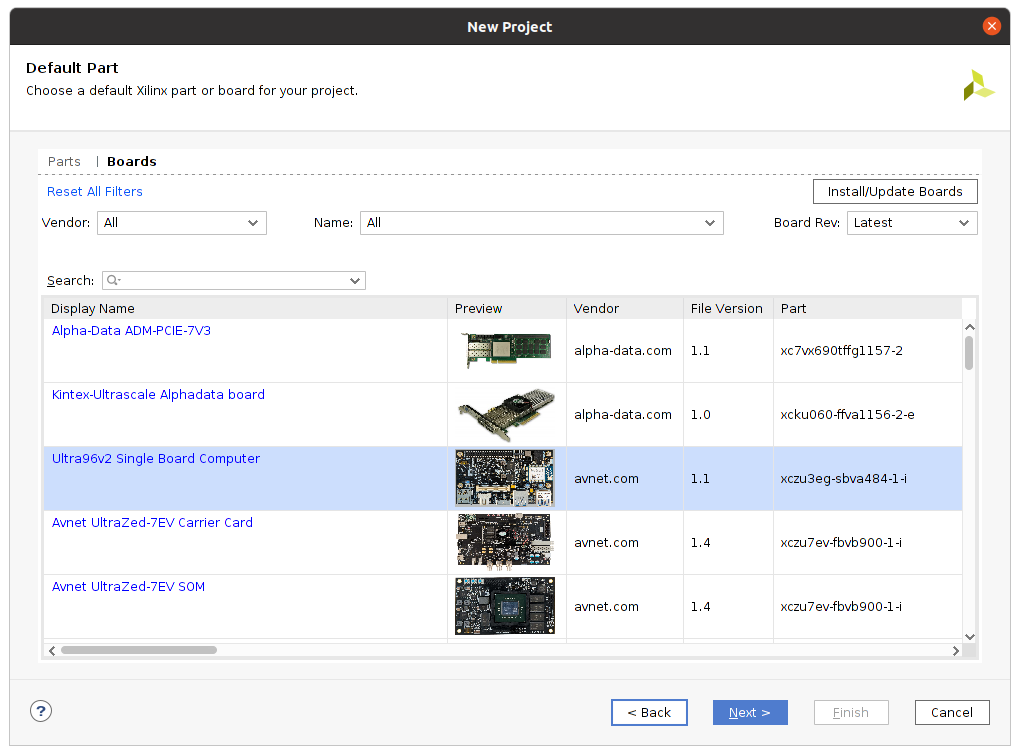

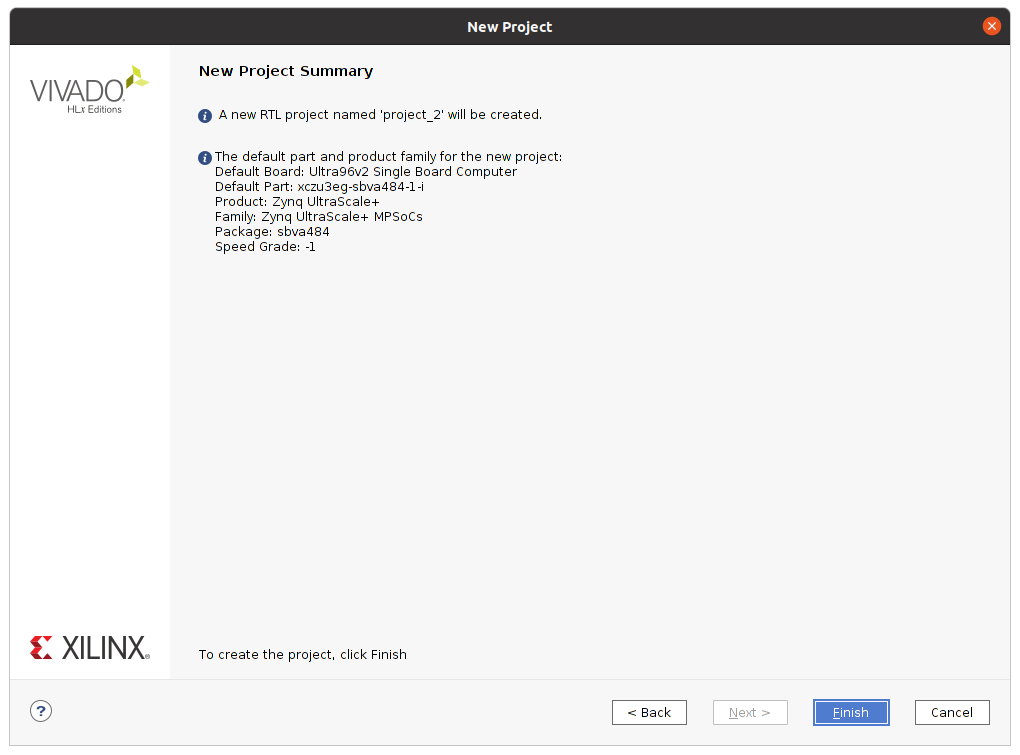

Boardをクリックして、Ultra96v2を選択して、Nextをクリックする。

Finishをクリックする

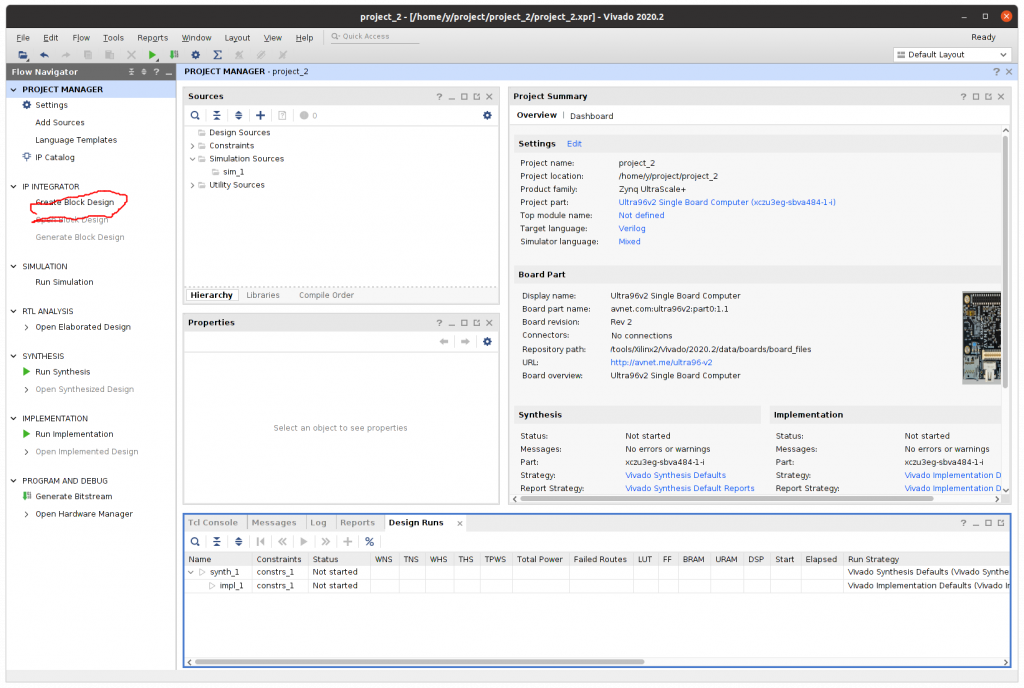

初期設定は終わりで、ここから実装していく。と言っても今回は、ほぼ空の実装になる。

Create Block Designをクリックする。

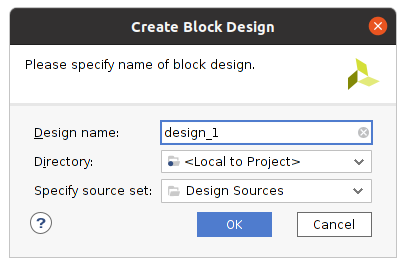

Create Block Designは、デフォルトのままOKをクリックする

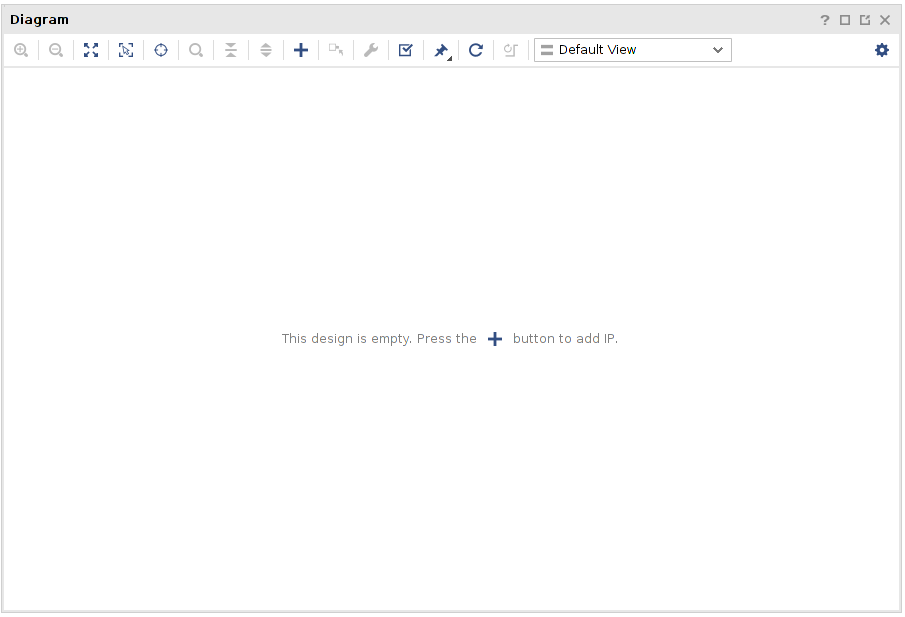

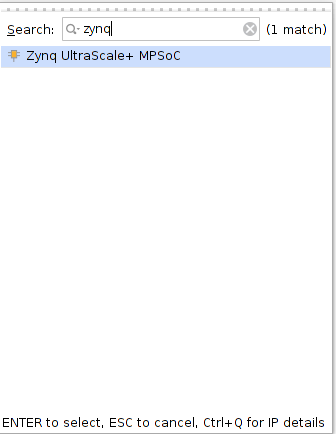

Diagramの+をクリックする

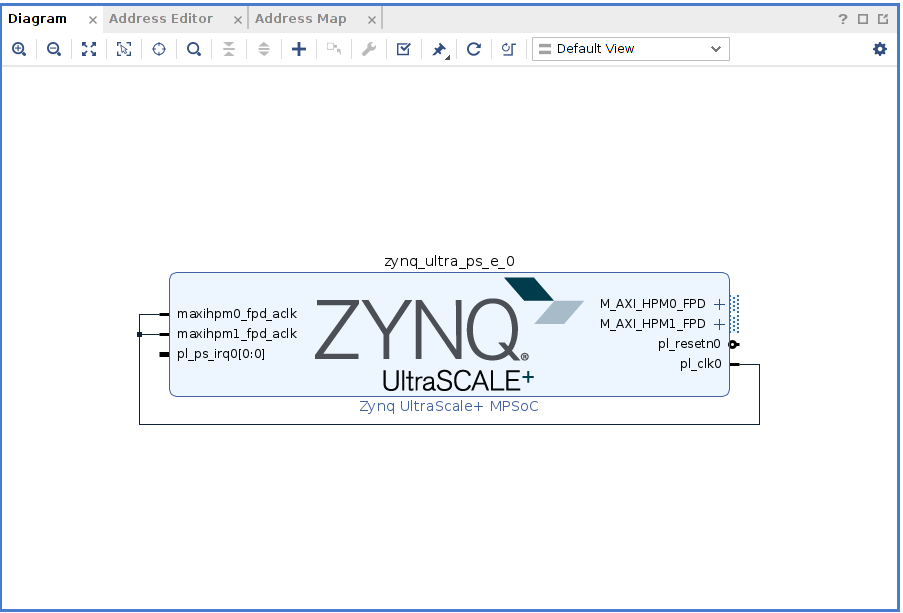

Searchにzynqと入力して、Zynq UltraScale+ MPSoCをクリックする

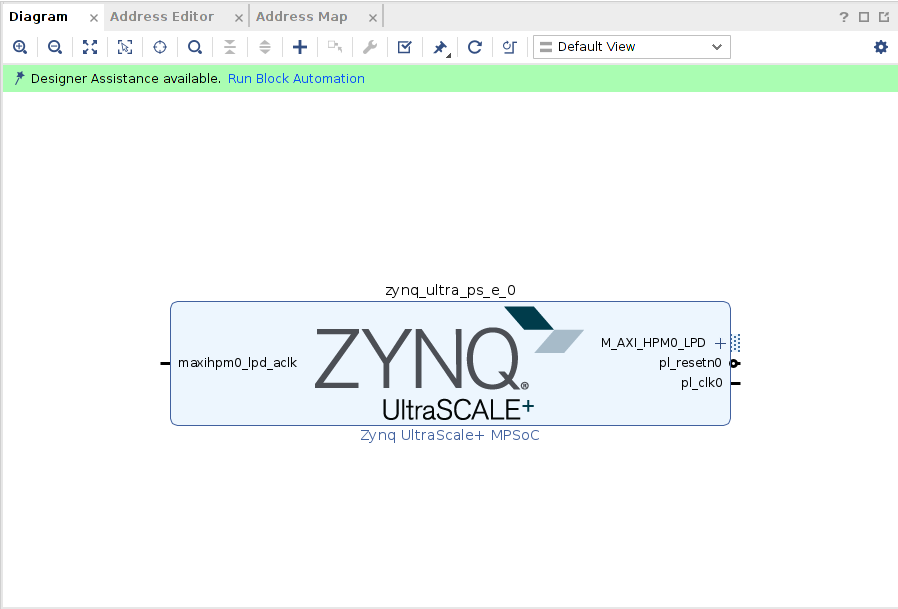

Zynqがあらわれて、Run Block Automationをクリックする

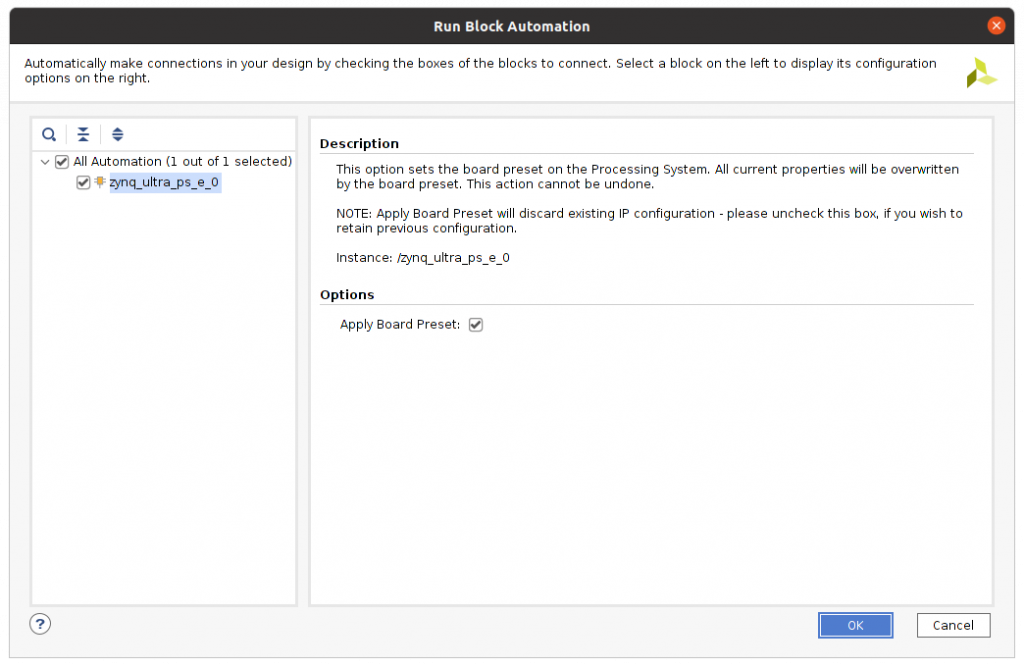

Apply Board Presetにチェックが入っている。OKをクリックする。

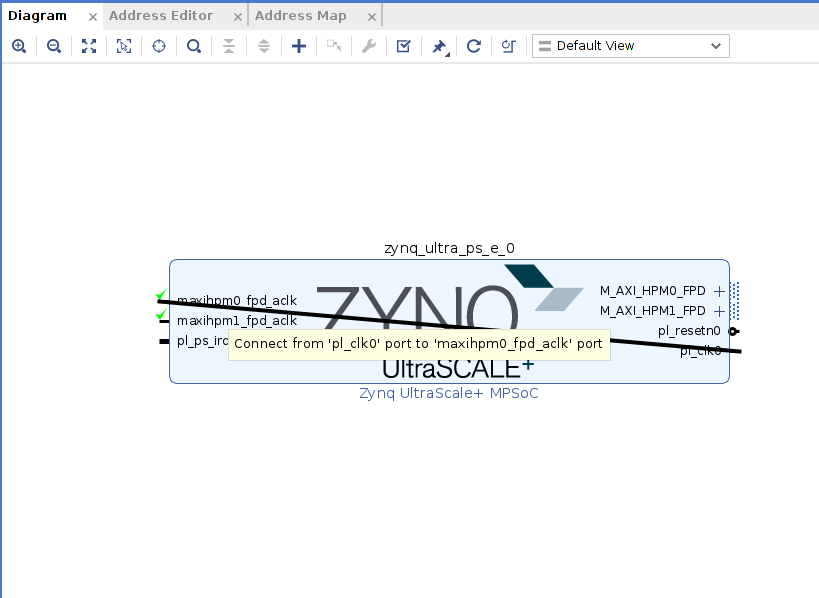

このままだとビルドエラーになるので、pl_clkとmaxihpm0_fpd_aclkとmaxihpm1_fpd_aclkをマウスでつなぐ。

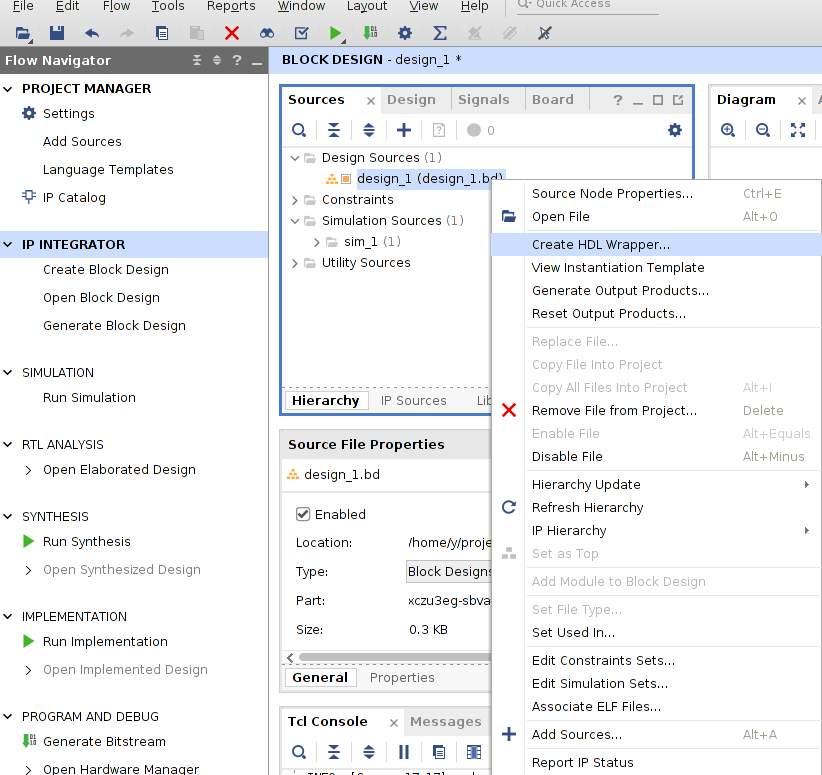

BLOCK DESIGNのSourceのDesign Source design_1を右クリックして、Create HDL Wrapperをクリックする

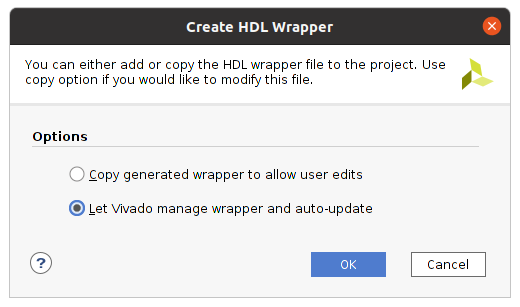

Let Vivado manage wrapper and auto-updateが選択されたまま OKをクリックする。

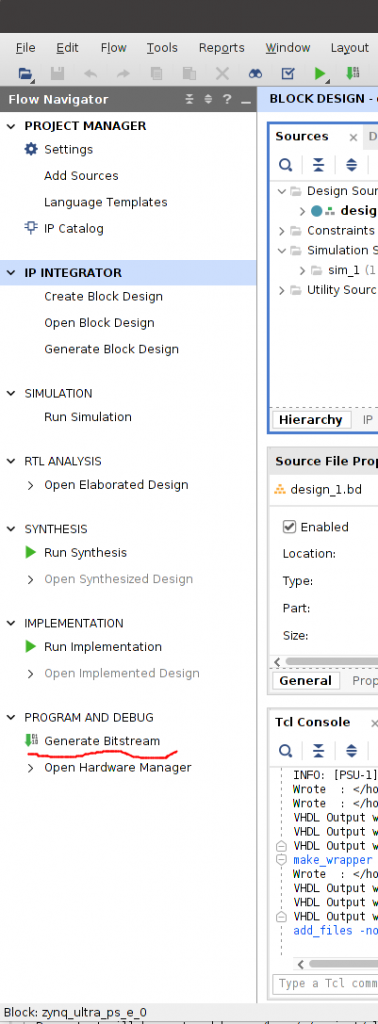

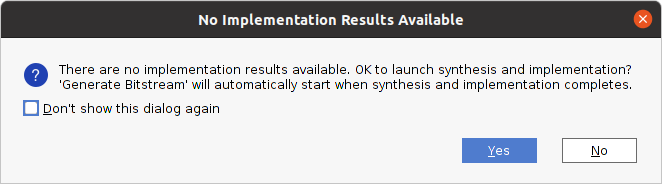

Generate BitStreamをクリックする

OKをクリックする

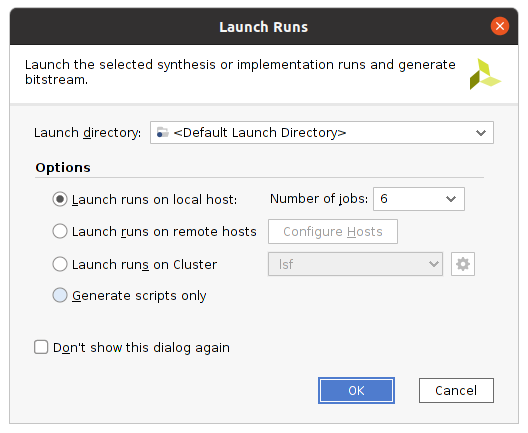

OKをクリックする

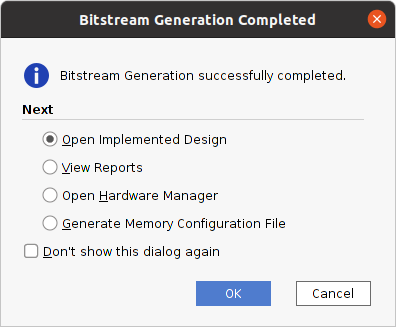

数分〜数十分で、Bitstreamの生成が終わると思う。終わったら今は特にすることがないので、キャンセルしておく。

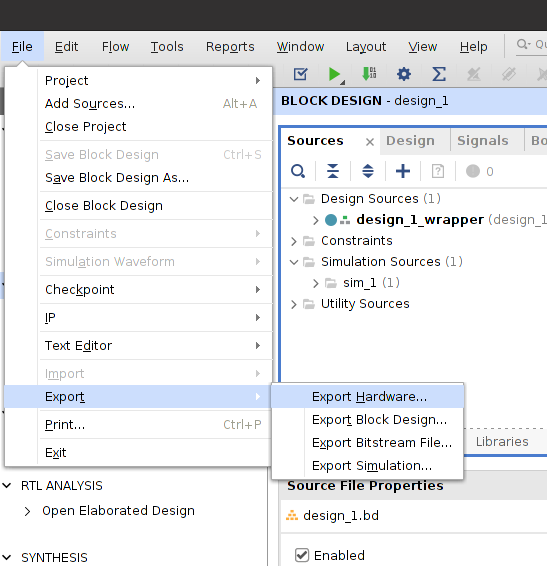

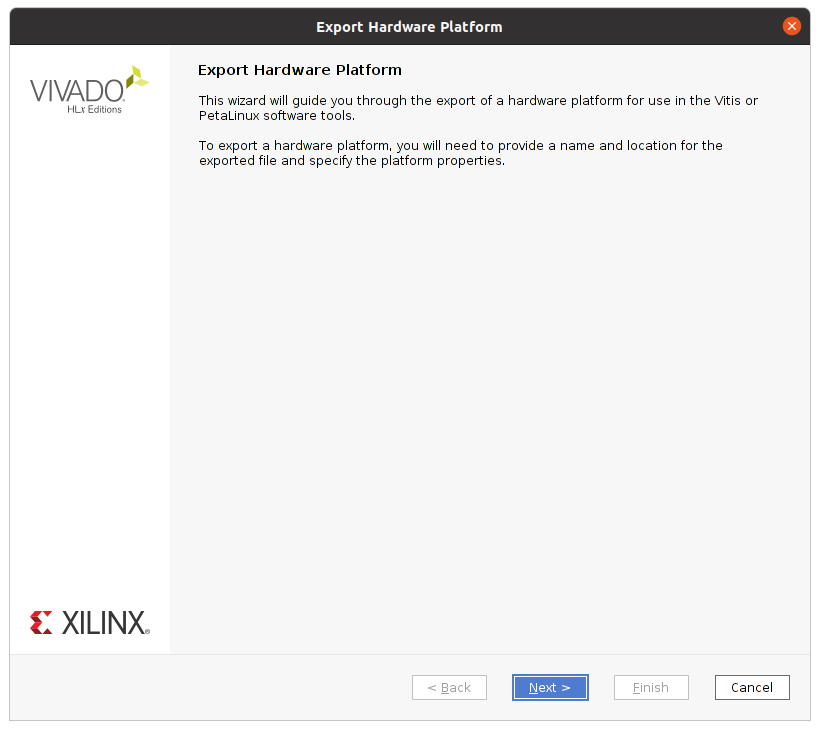

bitstreamをExportする。File→Export→Export Hardwareをクリックする。

Nextをクリックする。

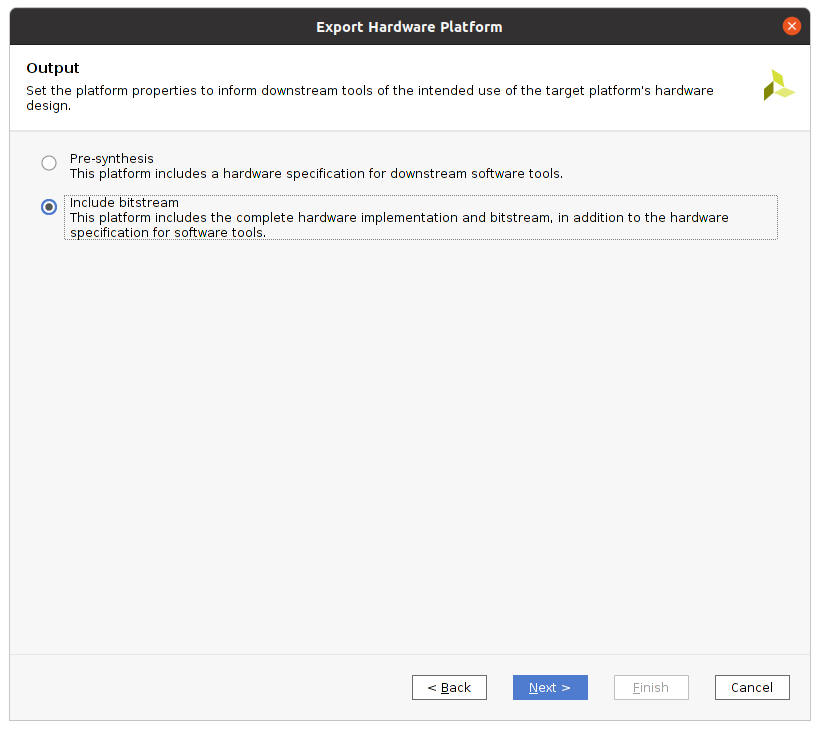

include bitstreamを選択して、Nextをクリックする

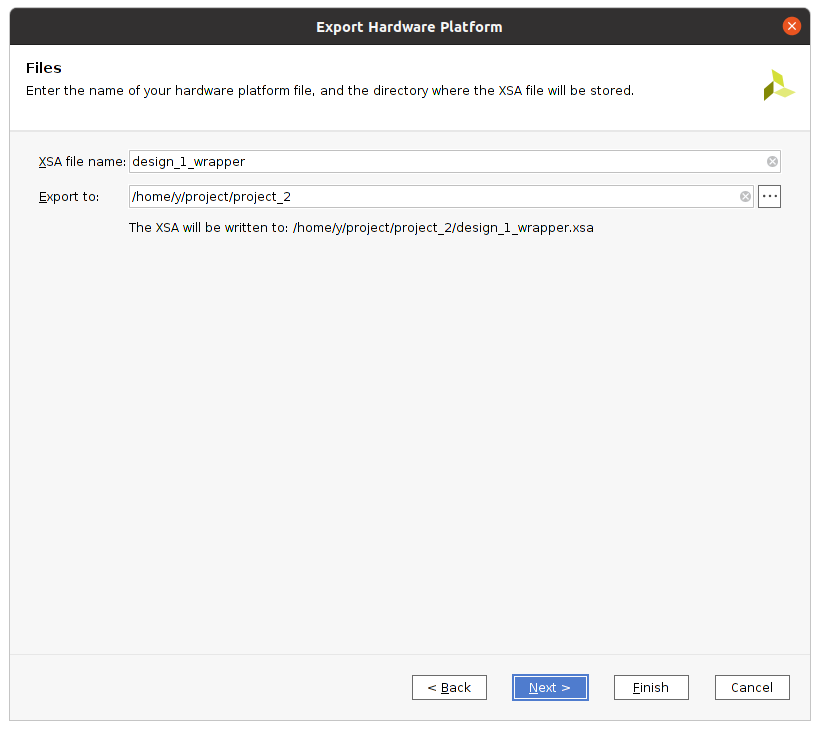

XSAファイル(Vitisでつかうファイル)の名前を設定して、Nextをクリックする

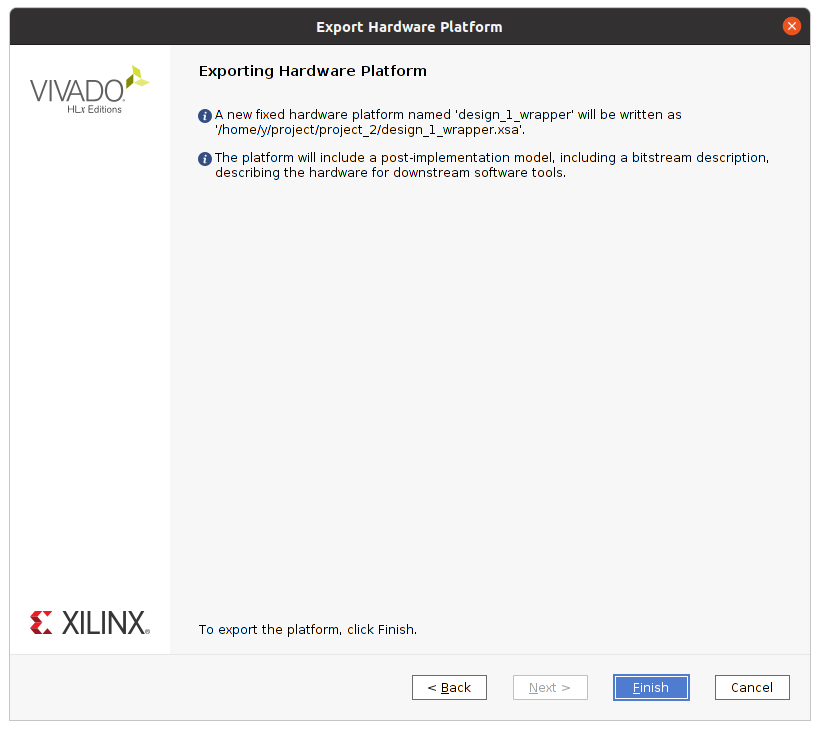

Finishをクリックする。終わり!

これで、ultra96のHW環境ができた。