Qiitaの以下のサイトの通りにkv260のPFを作成する。自分用メモ

https://qiita.com/basaro_k/items/e83128c265ae86801bbc

Vivado

Project name

kv260_hardware_platform

Project type

RTL Project。Project is an extensible Vitis Platformにチェック

Default Part

Boards→Kria KV260 Vision AI Starter Kit 。Connectionsで、Vision AI Starter Kit carrier cardを選択

IP INTEGRATOR

Create Block Desgin:Design nameにsystem

Block Diagram

Zynq UltraScale+ MPSoc

Run Block Auto mationをクリック→OKをクリック

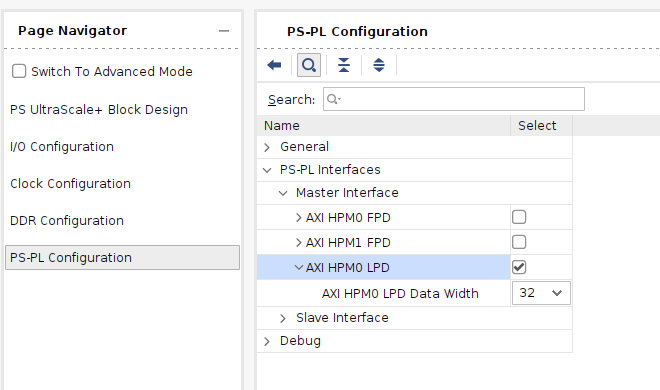

PS−PL Configuraiton で、

AXI HPM0 FPD チェックを外す

AXI HPM1 FPDチェックを外す

AXI HPM0 LPDチェックする32bitにする

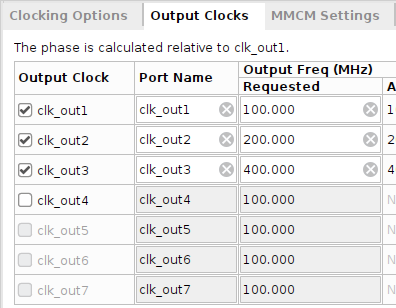

Clocking Wizerd

Outout Clocks

clk_out2,clk_out3をチェック。

clk_out2を200MHz,clk_out3を400MHzに設定

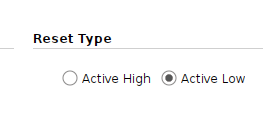

Reset TypeをActive Lowに設定

Processor System Reset

3個追加する。

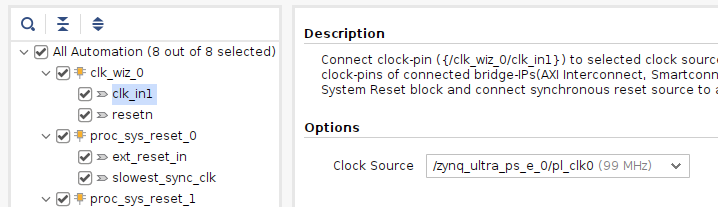

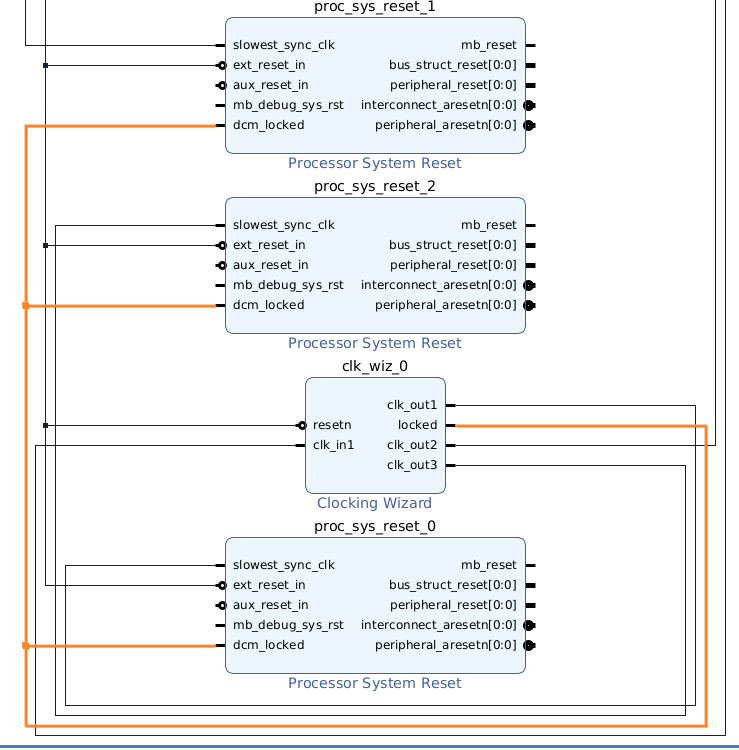

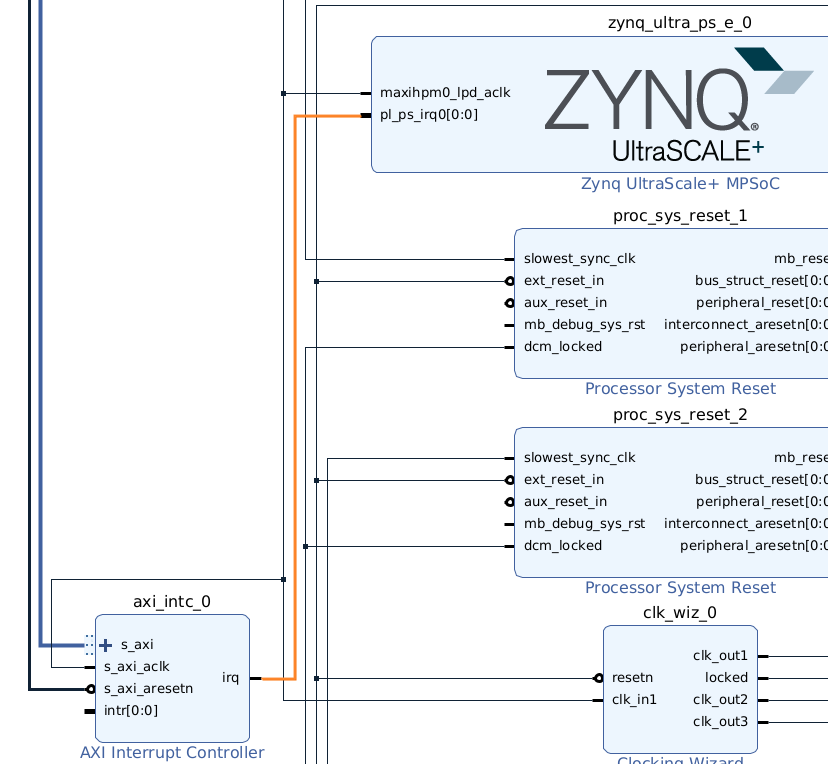

接続

Run Connection Automationをクリックする

clk_wiz_0のclk_in1に、zynq_ultra_ps_e_0/pl_clk0(99MHz)

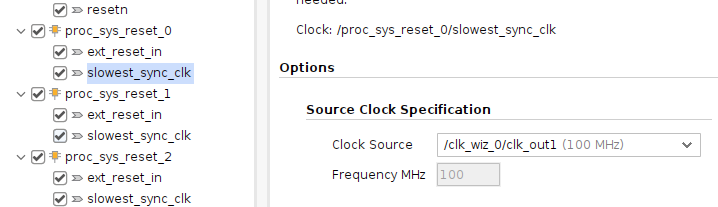

Proc_sys_reset_0のslowest_sync_clkに、clk_wiz_0/clk_out1(100MHZ)

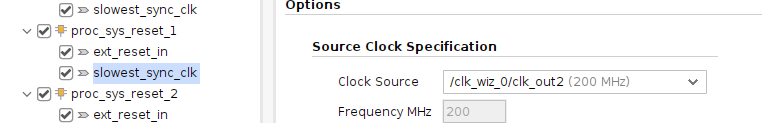

Proc_sys_reset_1のslowest_sync_clkに、clk_wiz_0/clk_out2(200MHZ)

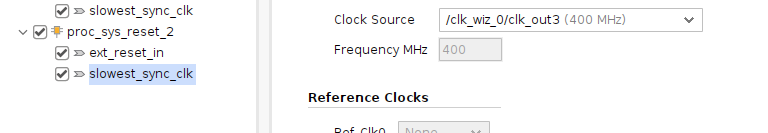

Proc_sys_reset_2のslowest_sync_clkに、clk_wiz_0/clk_out3(400MHZ)

clk_wiz_0のlockedを各resetのdcm_lockedに接続する

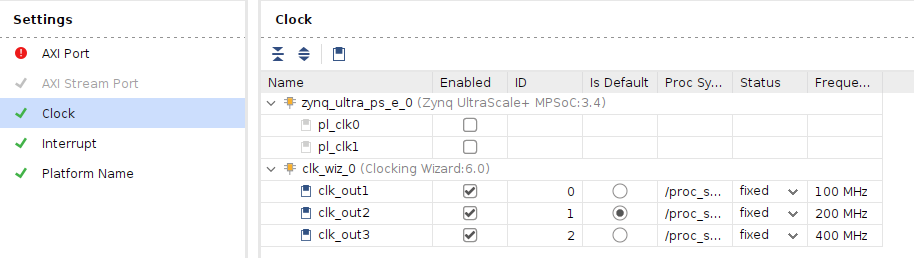

Vitis プラットフォームの設定 Clock

clk_out1,clk_out2,clk_out3にチェックを入れて、is Defaultは、clk_out2にチェックをいれる

AXI Interrupt Controller

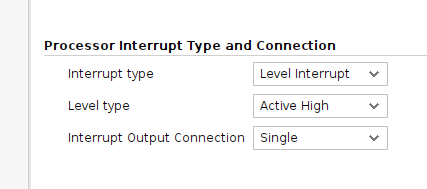

Processor Interrupt Type and Connection Interrupt Output ConnectionをSingleにする

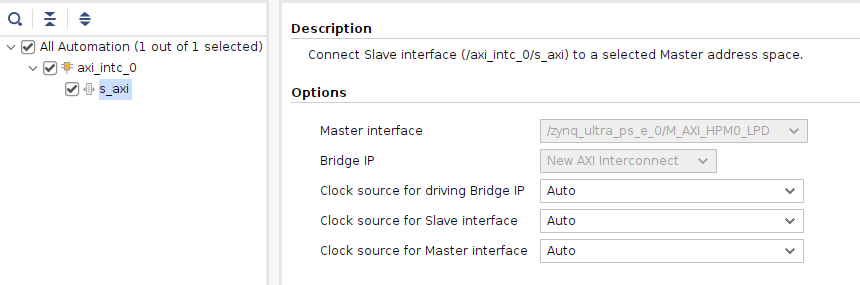

Run Connectoin Automationをクリックする→OKをクリックする

Zynq_ultra_ps_e_0のpl_ps_irq0[0:0]→axi_intc_0 irqをマウスで接続する

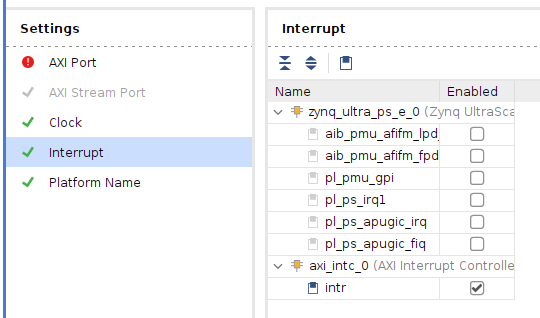

Vitis プラットフォーム設定 interrupt

axi_intc_0 intrをチェックする

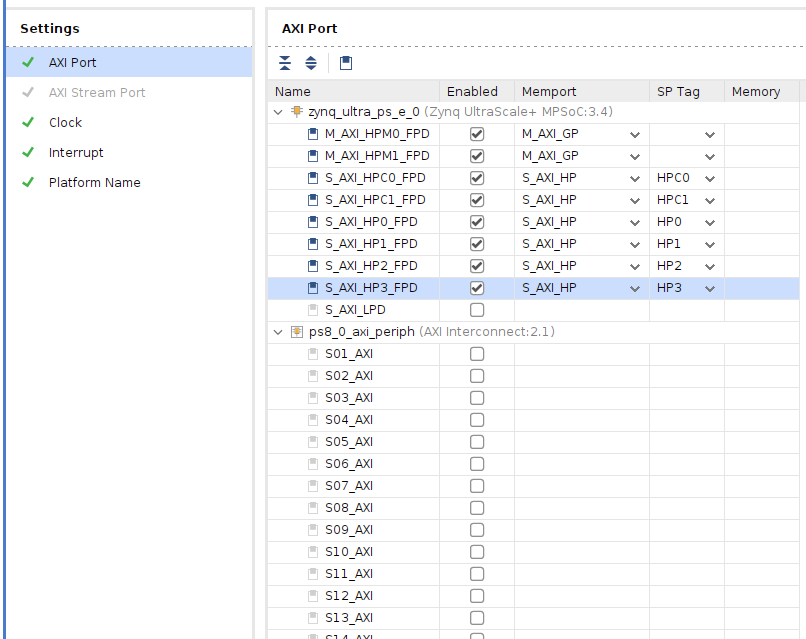

Vitis プラットフォーム設定 AXI Port

zynq_ultra_ps_e_0のS_AXI_LPD以外をチェックする。Memportは、S_AXI_HPC0_FPDと、S_AXI_HPC1_FPDをS_AXI_HPに変更する。

SP Tagは、S_AXI_HPC0_FPDは、HPC0

S_AXI_HPC1_FPDは、HPC1

S_AXI_HP0_FPDは、HP0

S_AXI_HP1_FPDは、HP1

S_AXI_HP2_FPDは、HP2

S_AXI_HP3_FPDは、HP3とする。SP Tagは、選択するように見えて、入力できる。

Create HDL Wrapper

systemをCreate HDL Wrapperする

Generate Bitstream

上記の設定ができたら、Generate Bitstreamする

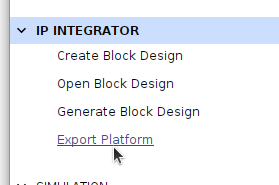

Export

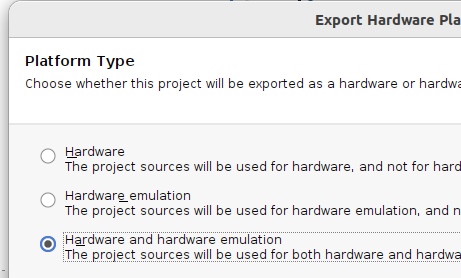

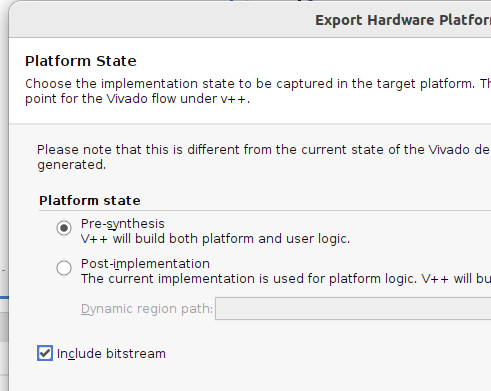

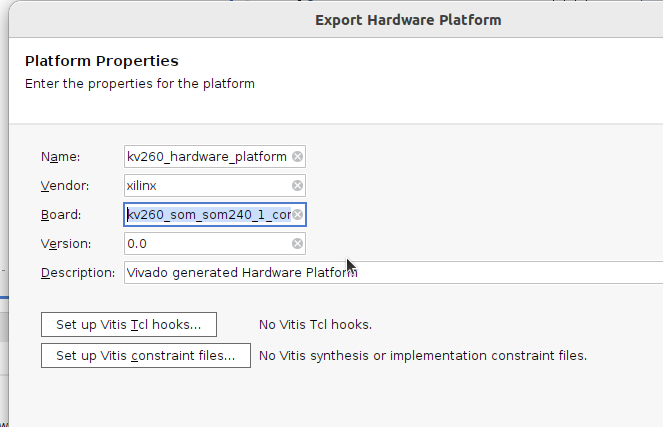

Export Platformをクリックする。Hardware and hardware emulationをクリック。

Pre-sysnthesisを選択して、include bitstreamにチェック

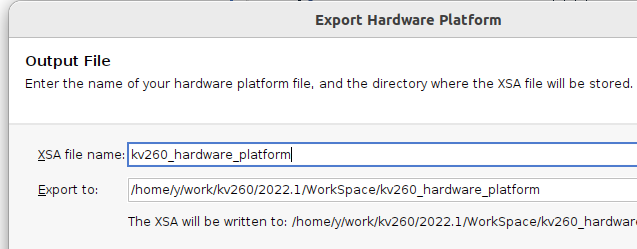

XSAのファイル名をkv260_hardware_platformに設定する。finishする

生成されたxprとxsaファイルを使用する

生成されたProjectを以下に保存した