z-turnでVitis HW Platformを作成する。以下の動画を参考にしている

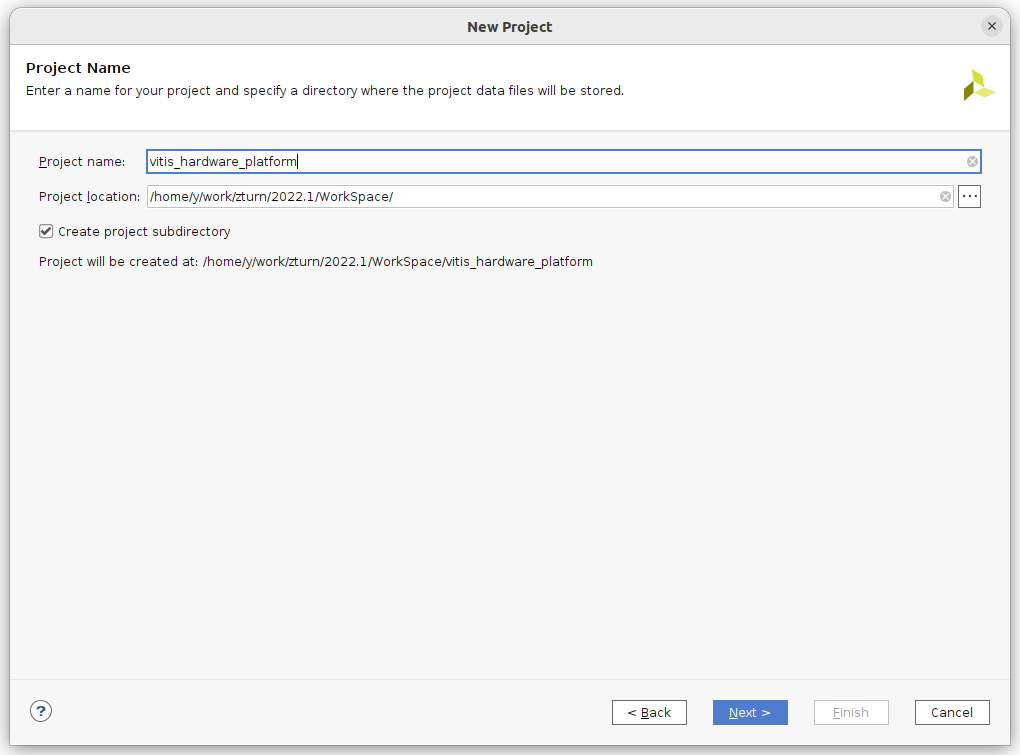

プロジェクトの作成

ディレクトリと、プロジェクト名を指定して、Nextをクリックする

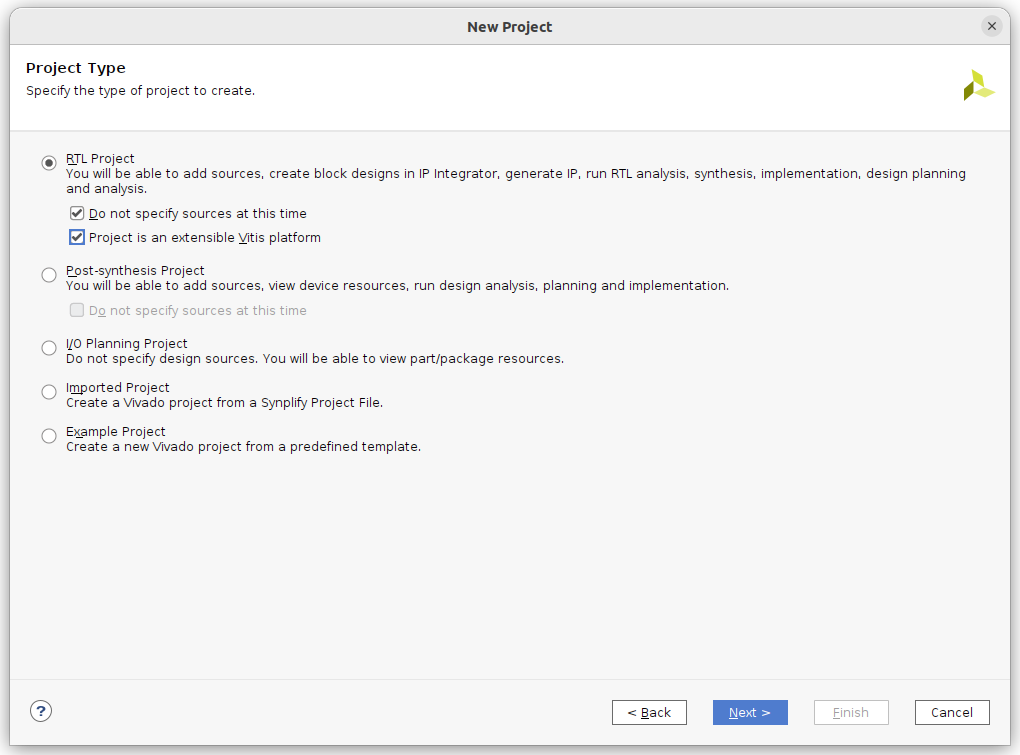

Project is an extensible Vitis platromにチエックして、Nextをクリックする

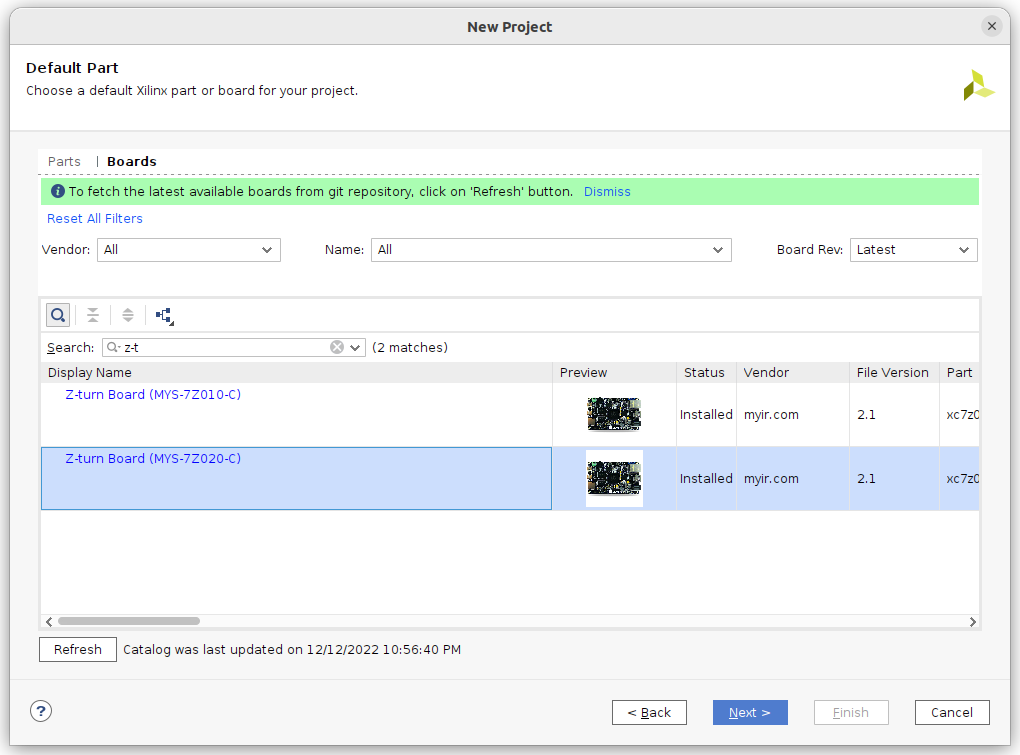

Boardをクリックして、z-turn Board (MYS-7Z020-C)を選択して、Nextをクリックする。Boardの情報がない時は、以下の記事を参考にする

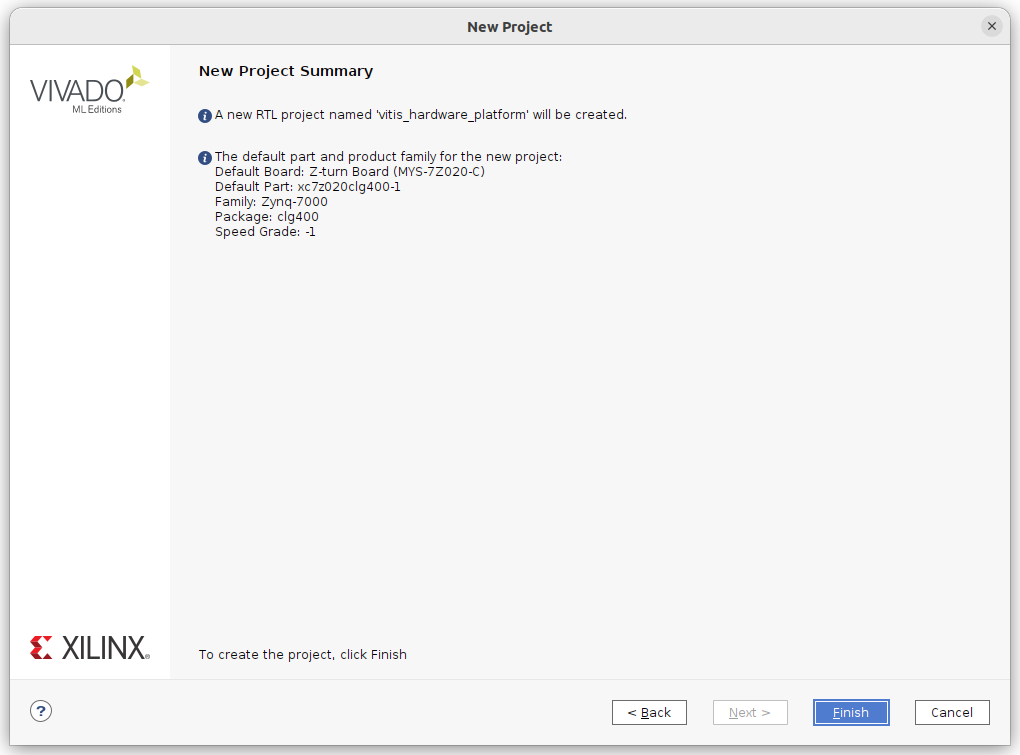

Finishをクリックする

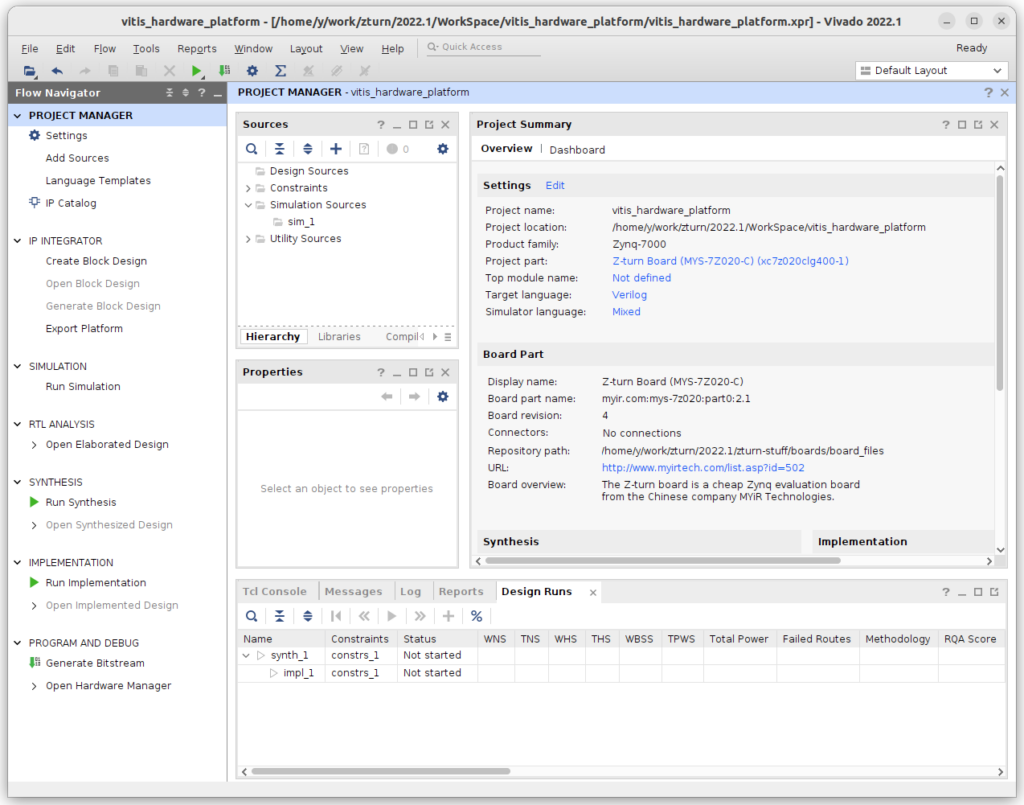

プロジェクトが生成された

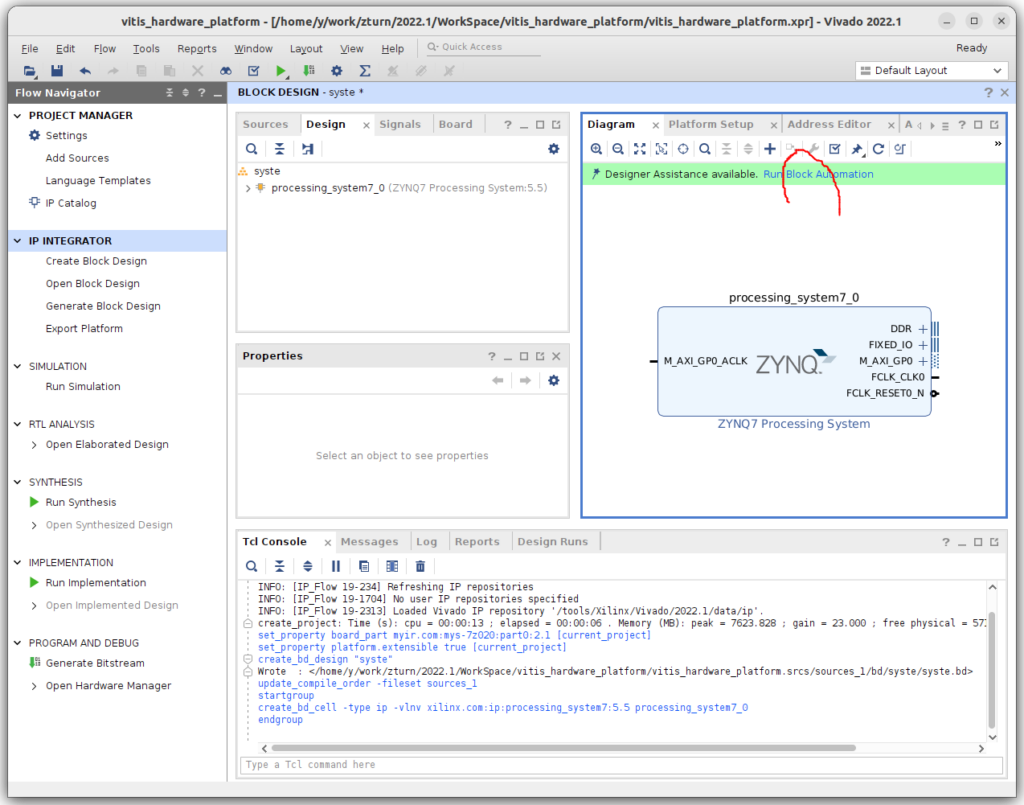

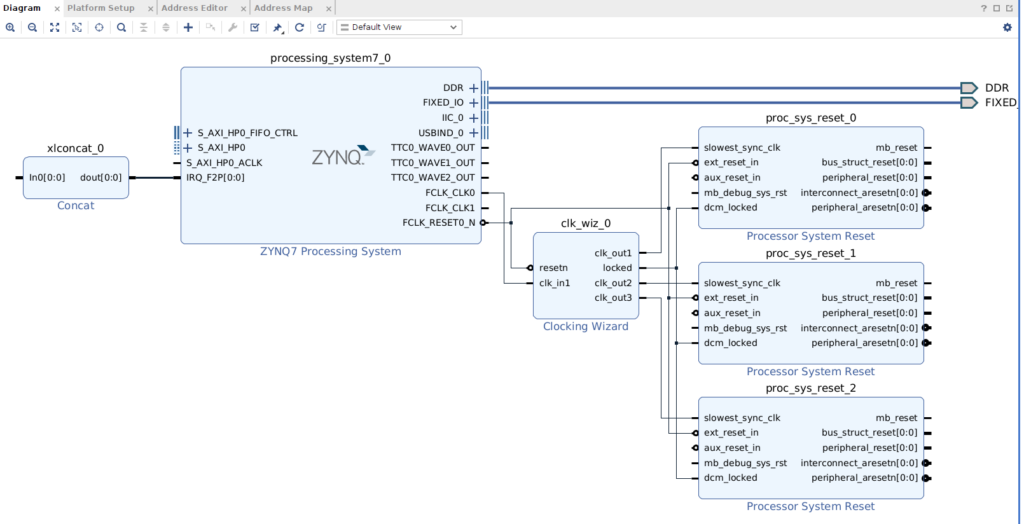

ブロックデザインの作成

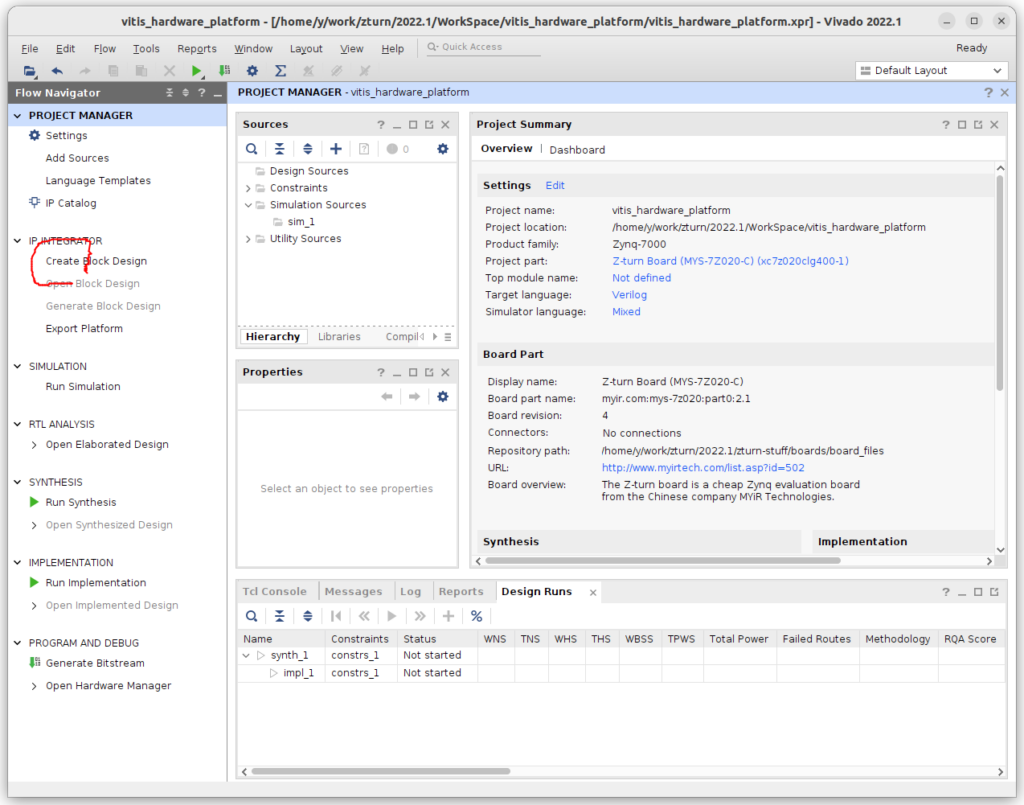

Create Block Designをクリックする

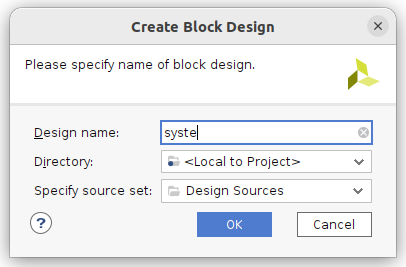

Design nameにsystemと入力して、OKをクリックする

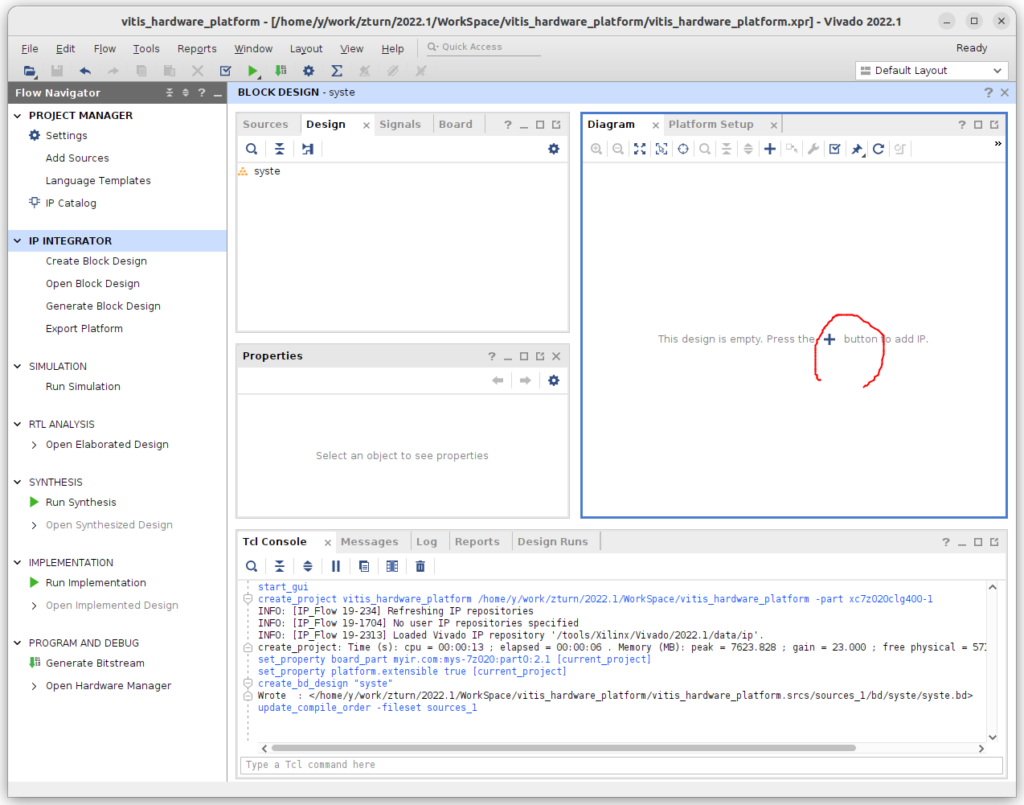

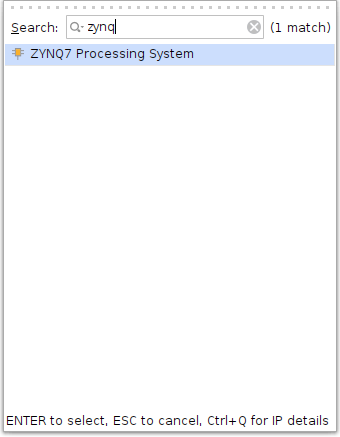

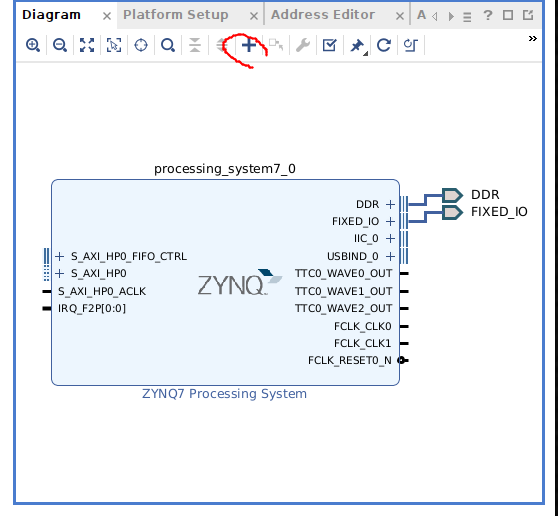

Diagramで+をクリックする

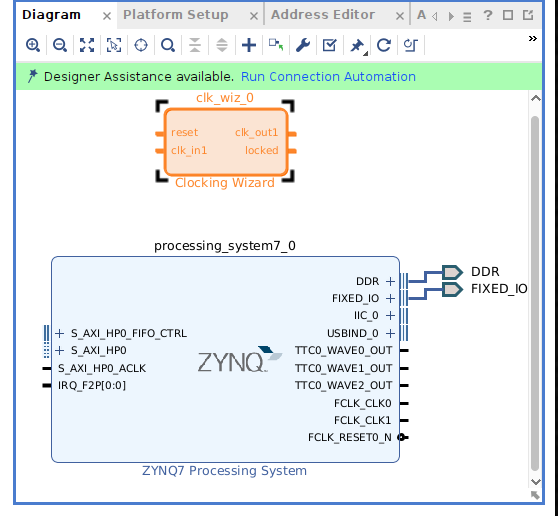

ZYNQ7 Processing Systemをクリックする

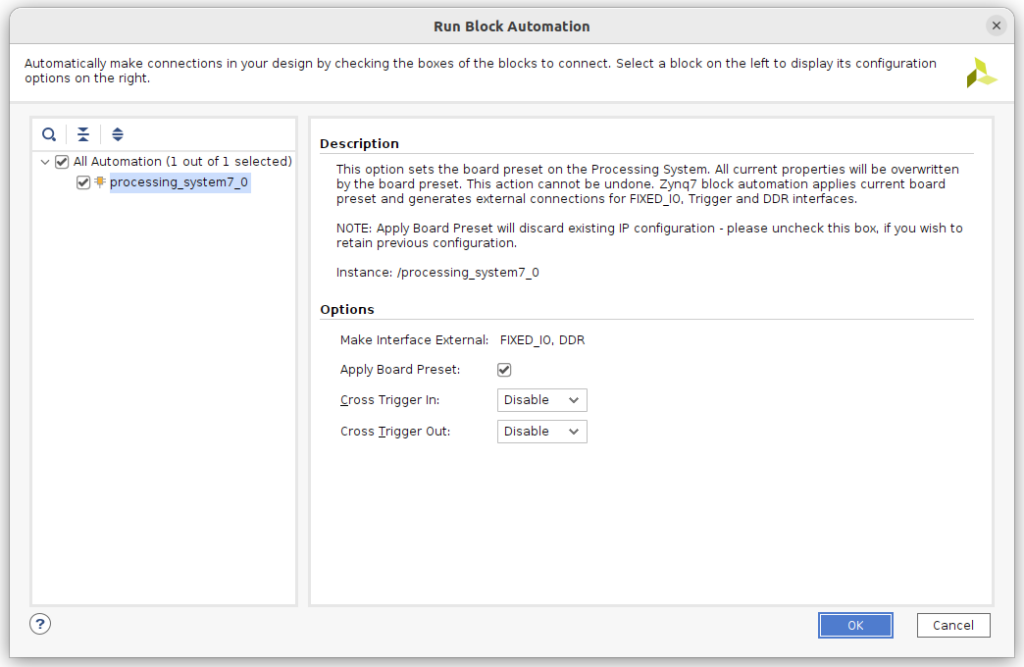

Run Block AUtomationをクリックする

OKをクリックする

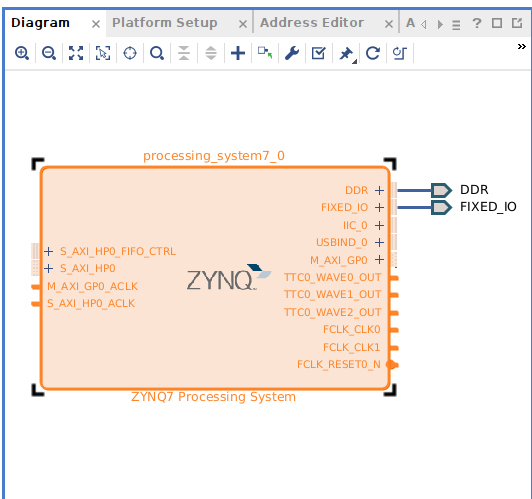

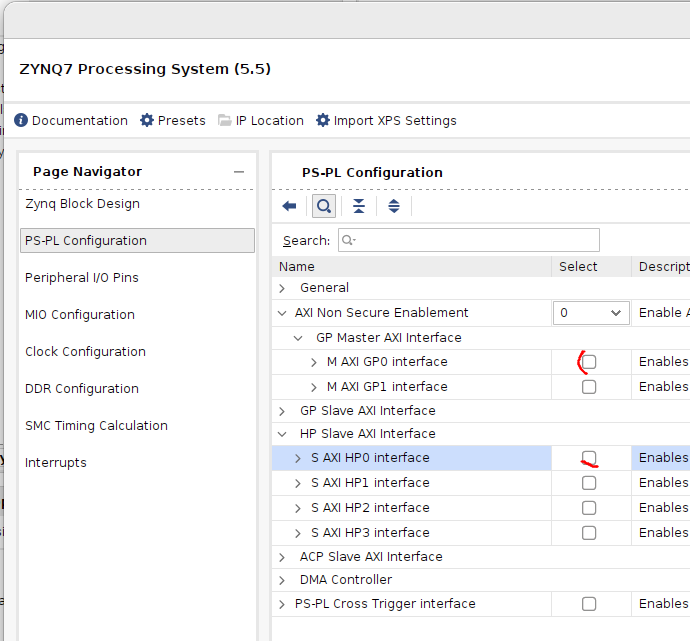

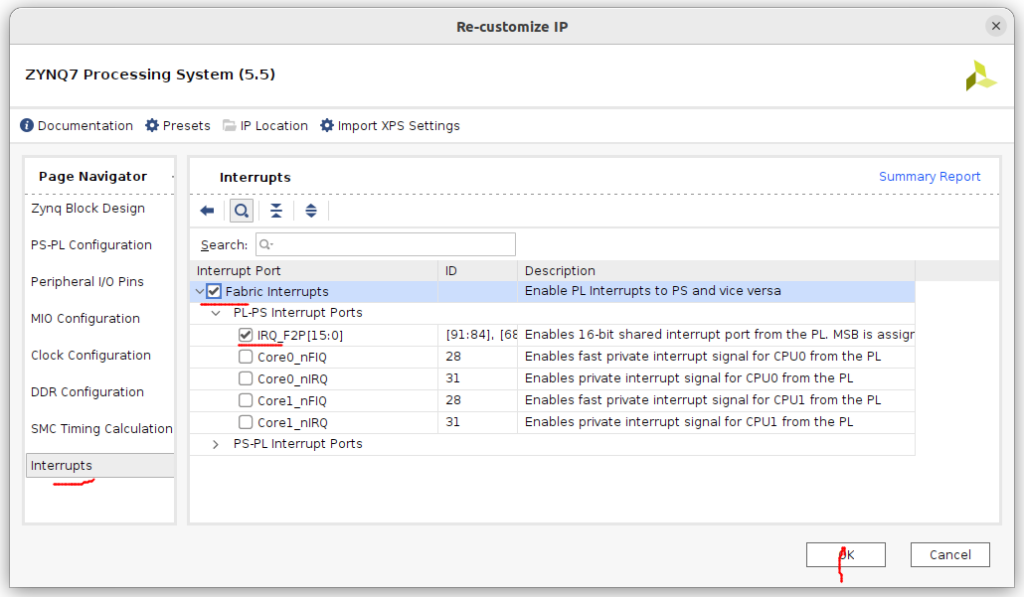

ZYNQをクリックして、Re-customize IPの画面を表示する

PS-P Congigurationをクリックして、AXI Non Secure Enalement -> GP Master AXI Interface -> M AXI GP0 interfaceのチェックをはずす。

HP Slave AXI Interface -> S AXI HP0 interfaceのチェックも外す

Interrutp -> Fabric interruptsにチェックする -> PL-PS interrupt Ports -> IRQ F2Pにチェックがあることを確認する。OKをクリックする

+をクリックする

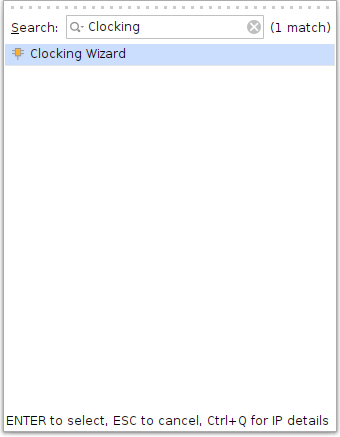

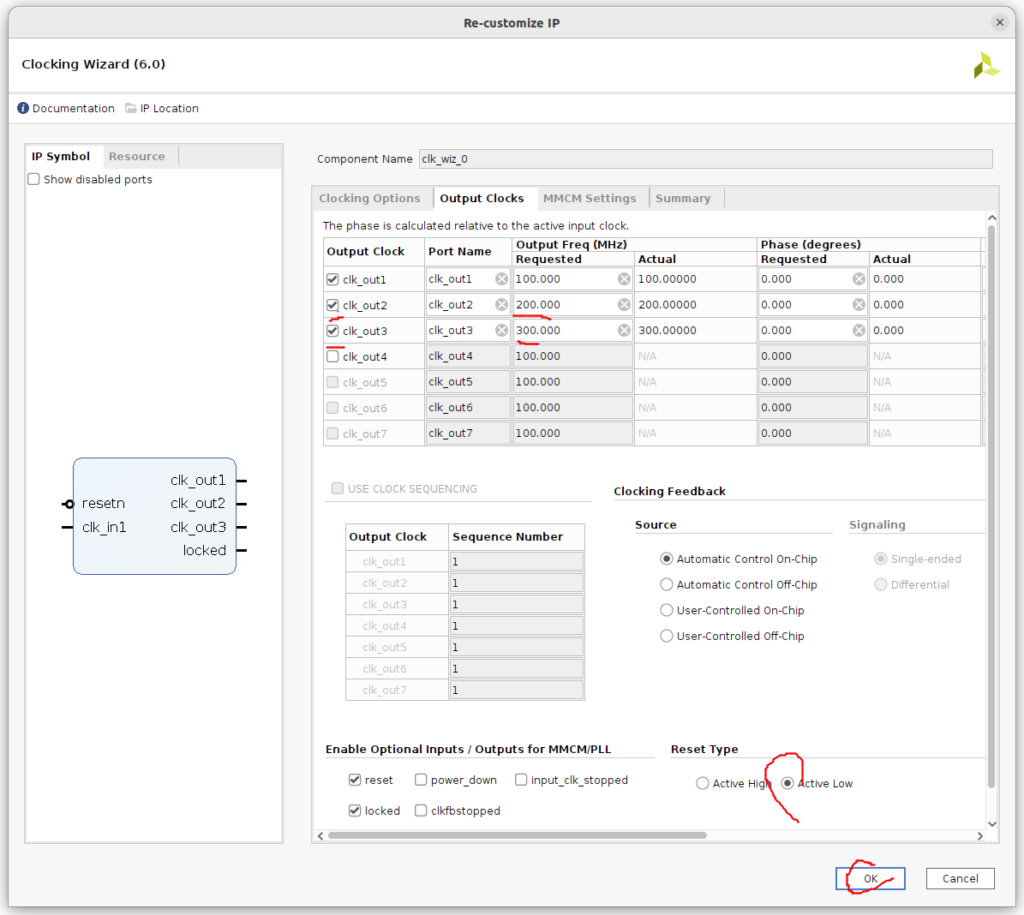

Clocking Wizrdをクリックする

Clocking Wizardをクリックする

Output Clockのタブをクリックして、Output clock 列のclk_out2,clkout3をチェックを入れて、Output Freqに200、300を入力する。Reset TypeはActive Lowをクリックする。OKをクリックする

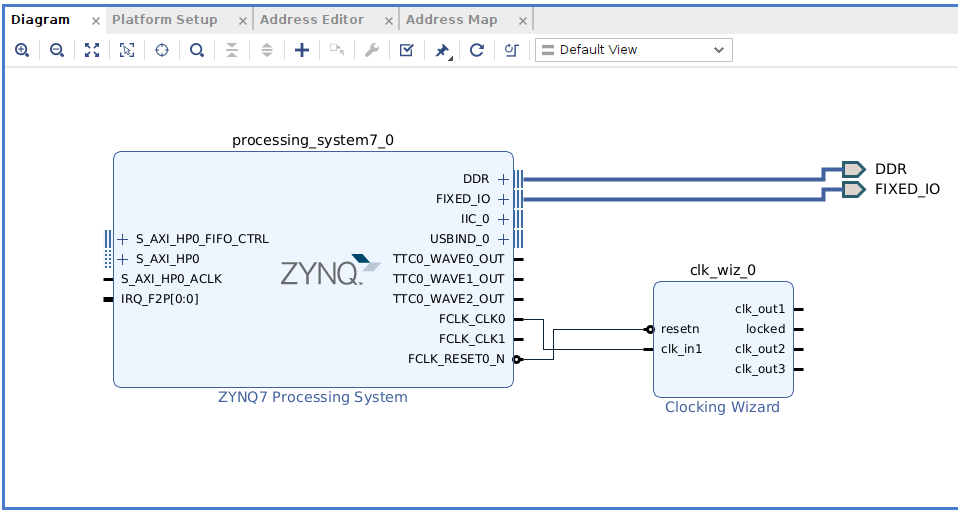

Clockig WizardとZYNQのFCLK_CLK0とclk_in1,FCLK_RESET0_Nとresetnを接続する

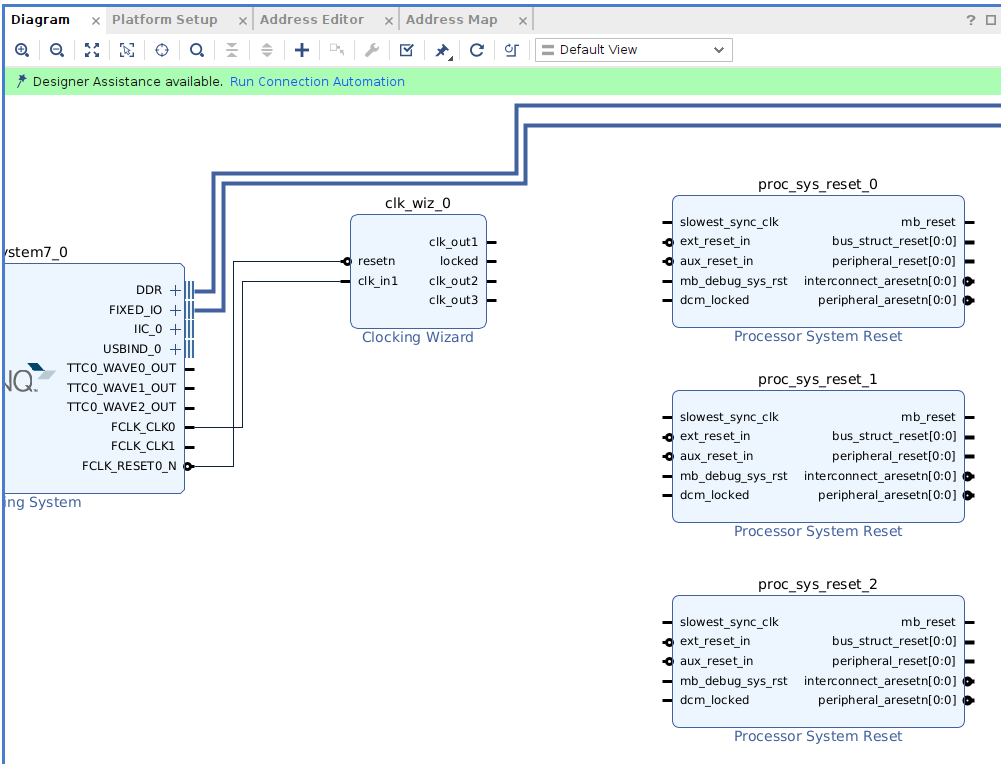

+をクリックして、Processer System Resetを3個追加する

Clocking Wizardのclk_out1,clk_out2,clk_out3を各Processor System ResetのSlowest_sync_clkに接続する。lockedを各Processor System Resetのdcm_lockedを接続する。ZYNQのFCLK_RESET0_Nを各Processor System Resetのext_reset_inに接続する

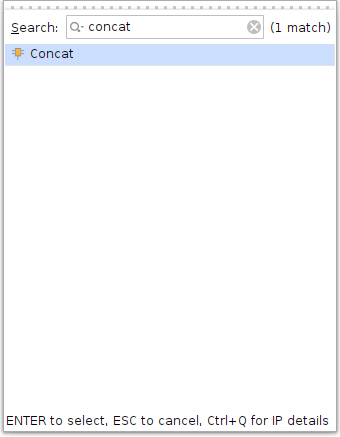

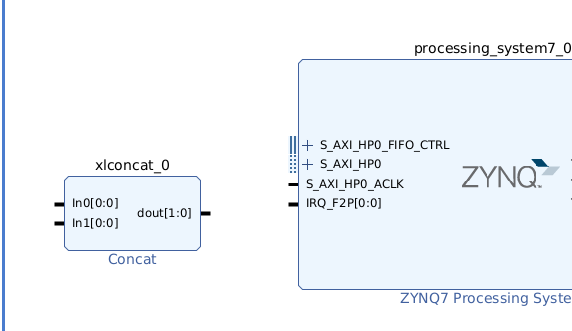

+をクリックして、concatを追加する

Concatをクリックする

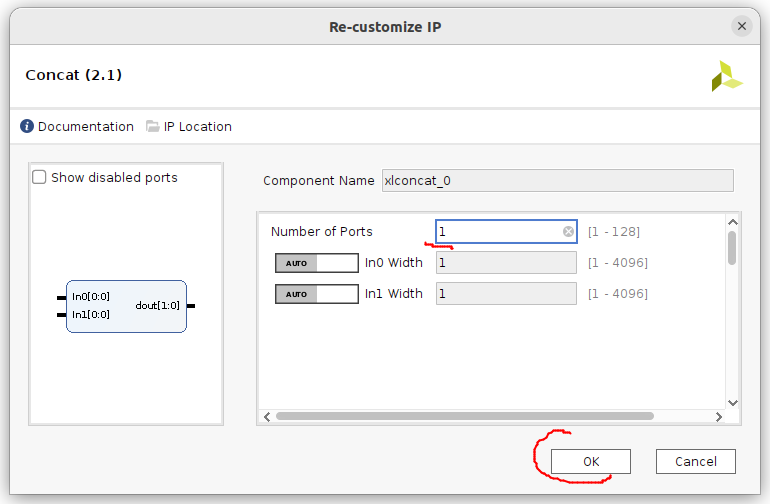

Number of Portを1にする。OKをクリックする

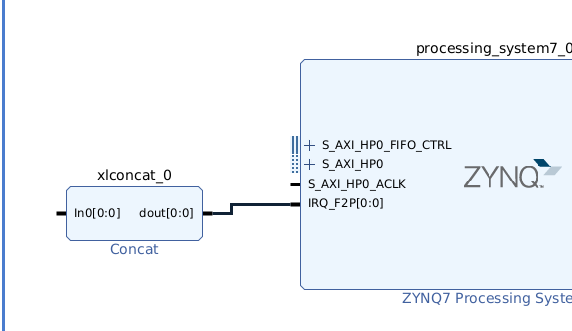

ConcatのdoutとZYNQのIRQ_F2Pを接続する

ブロックデザインができた

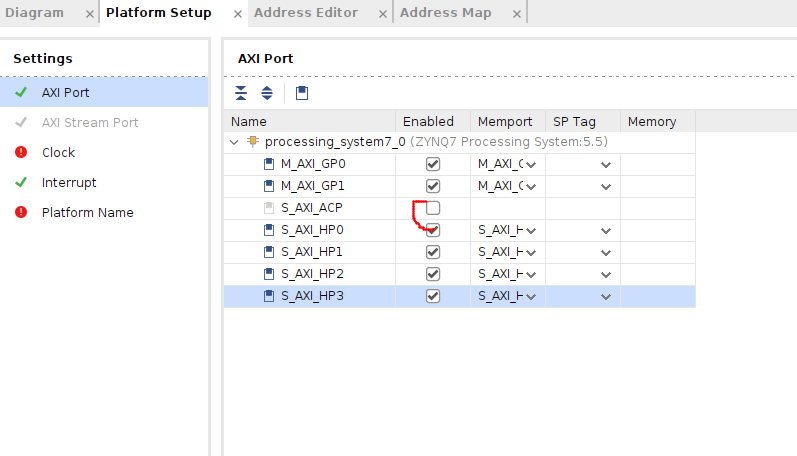

プラットフォームの設定

Platform Setupをクリックして、AXI Portをクリックする。S_AXI_ACP以外をEnableにする

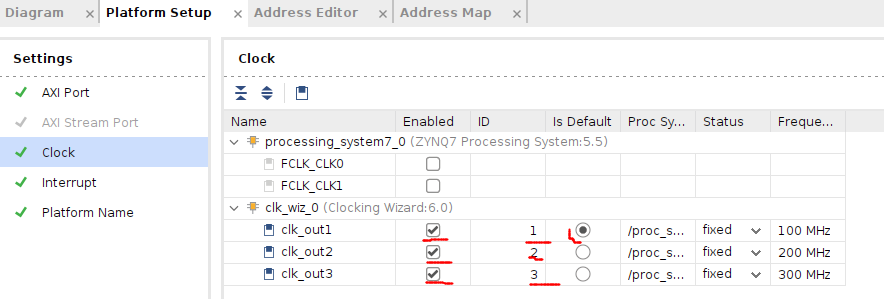

Clockをクリックして、clk_out1,clk_out2,clk_out3をEnabledにして、IDを1,2,3に変更して、clk_out1をIs Defaultにチェックする

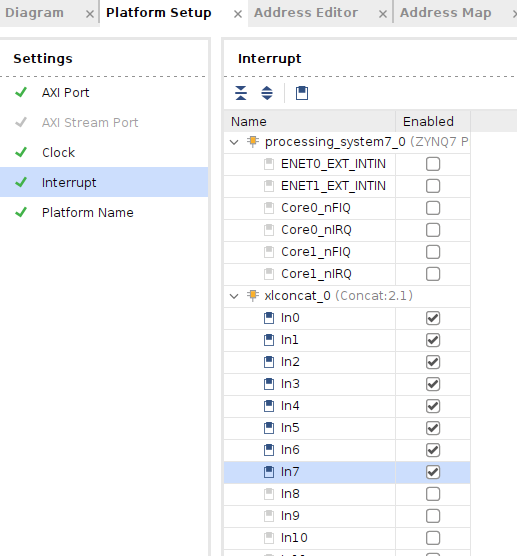

Interruptをクリックして、in0からIn7をEnabledにチェックする

ビルド

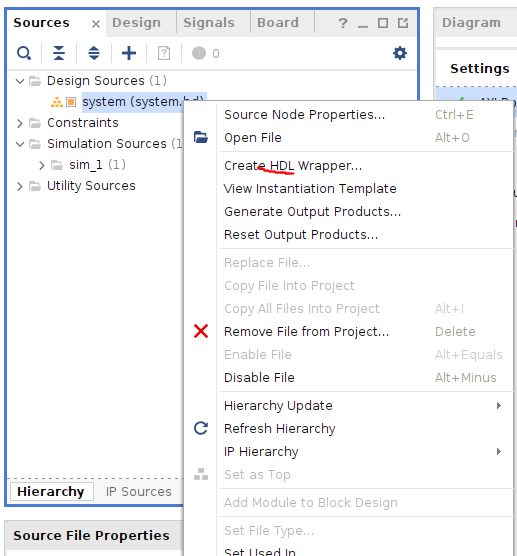

Source ->Design Sources ->systemで右クリックして、Create HDL Wrapperをクリックする

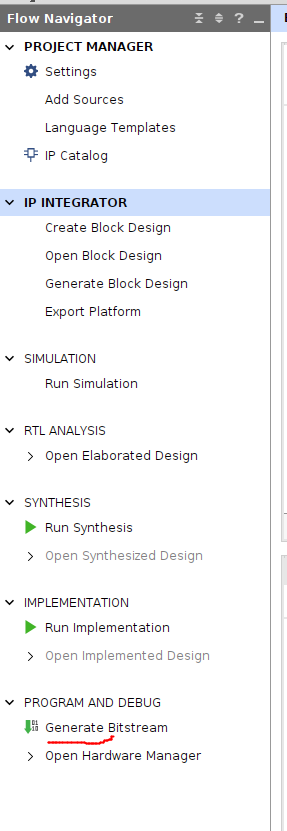

Gnerate Bitstreamをクリックする

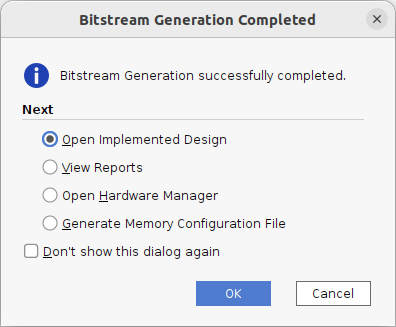

ビルドが完了した。キャンセルする

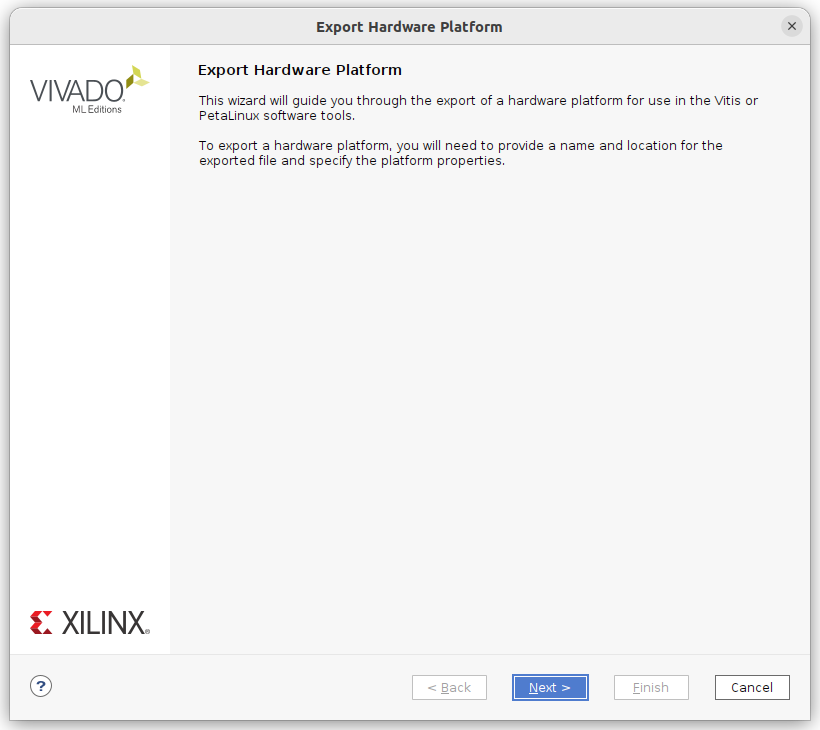

ハードウェアデザインのexport

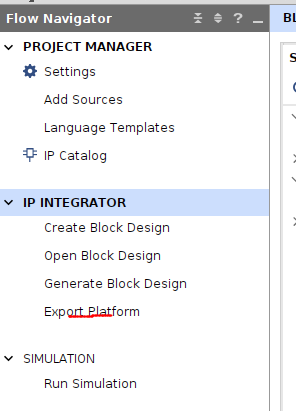

Export Desginをクリックする

Nextをクリックする

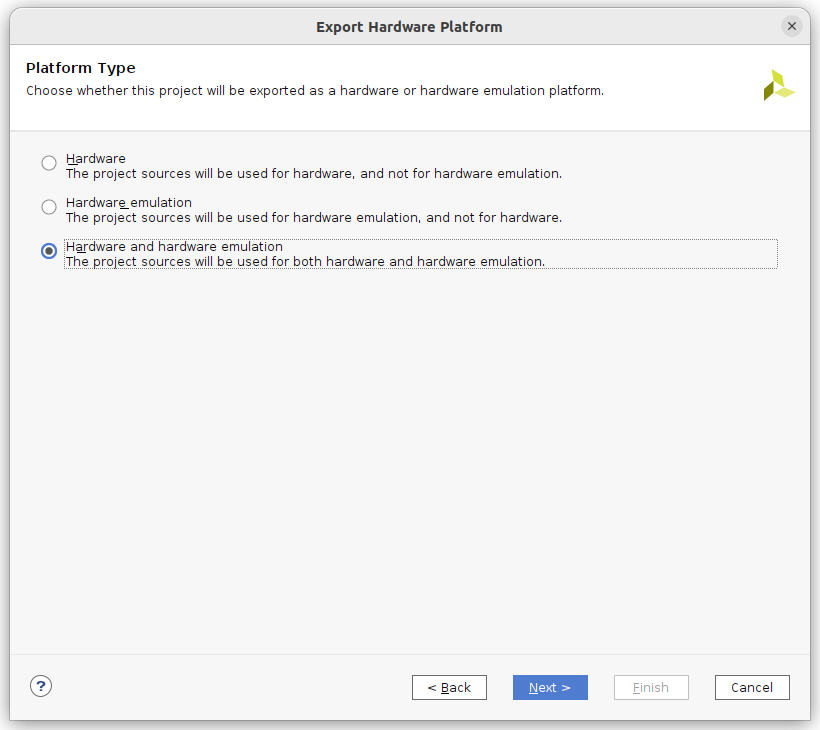

Hardware and hardware emulationをクリックする。Nextをクリックする

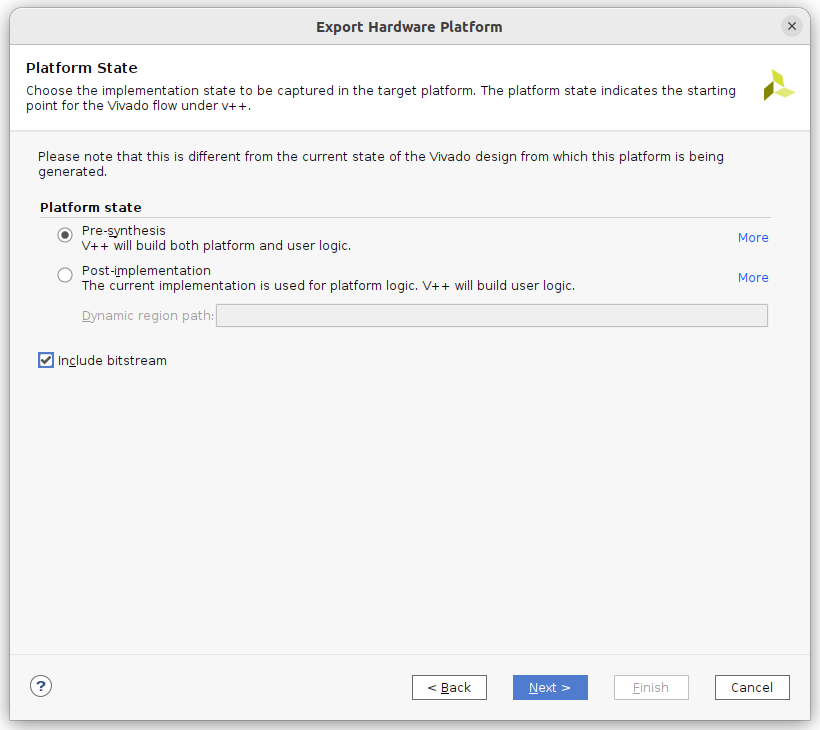

include bitstreamにチェックして、Nextをクリックする

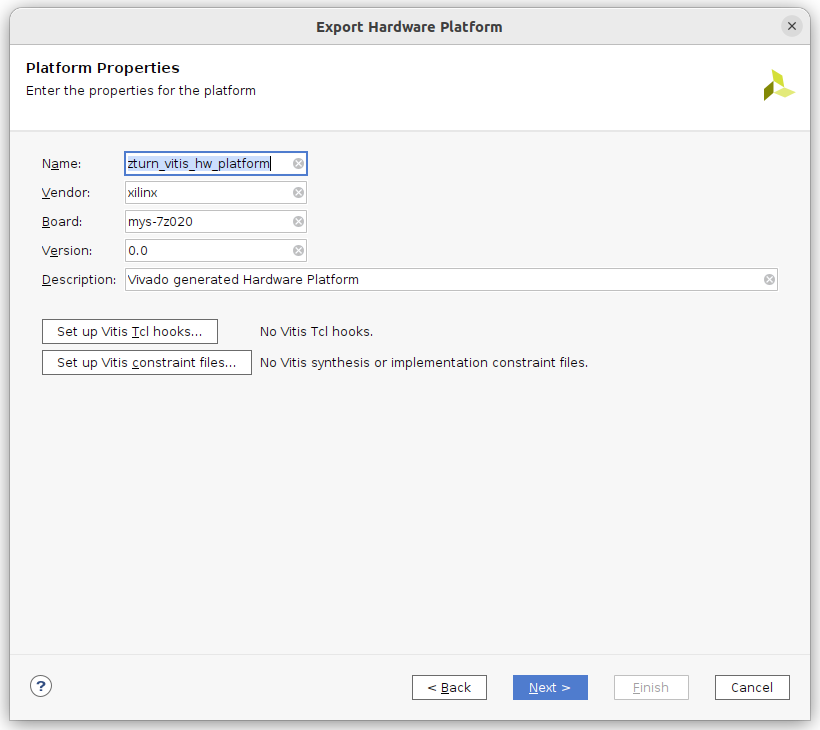

Nameに、zturn_vitis_hw_platformと入力して、Nextをクリックする

Nextをクリックする

Finishをクリックする

生成されたxprとxsaとbitファイルを使用する

system_wrapper.xsa

vitis_hw_platform.xpr

vitis_hw_platform.runs/impl_1/system_wrapper.bit