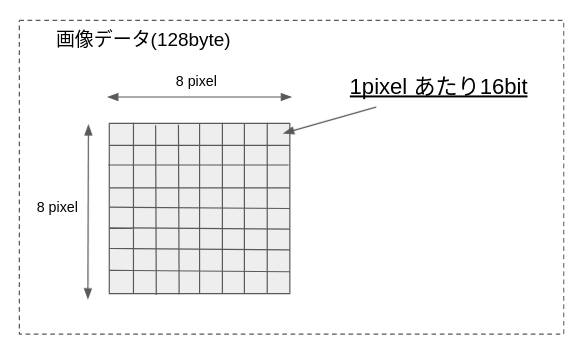

FPGAで、8×8の画像処理を実施する。以下のような画像を処理する。

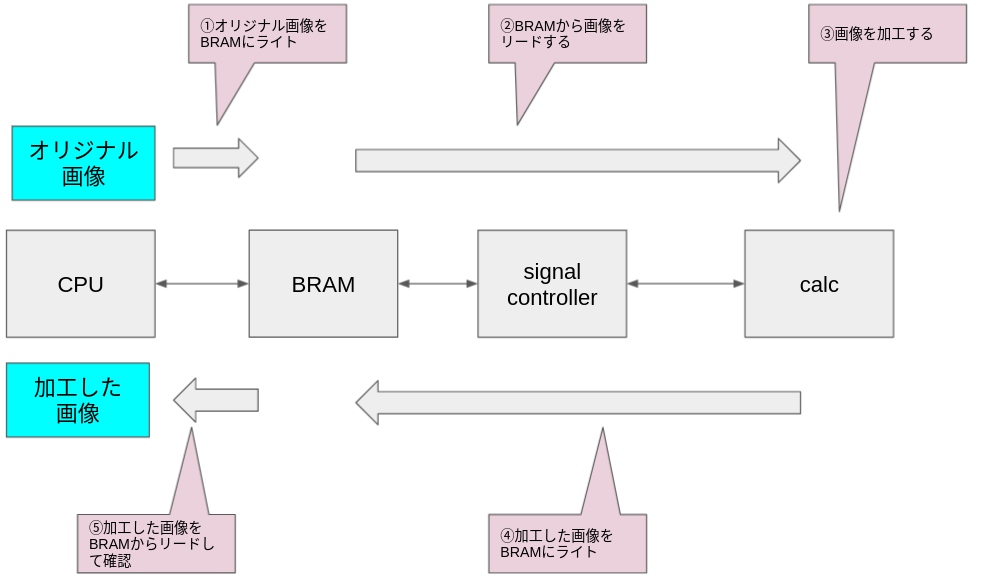

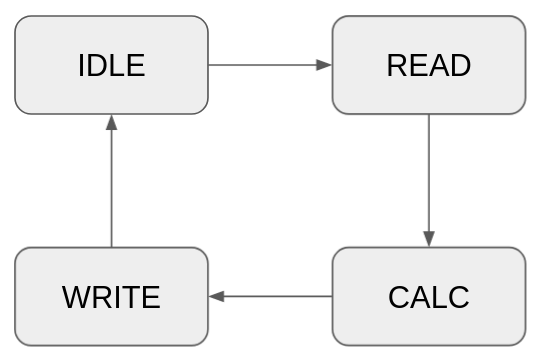

処理の流れは、以下のような感じだ。

デバイスは、Zynqで、評価ボードは、Ultra96を使っている。

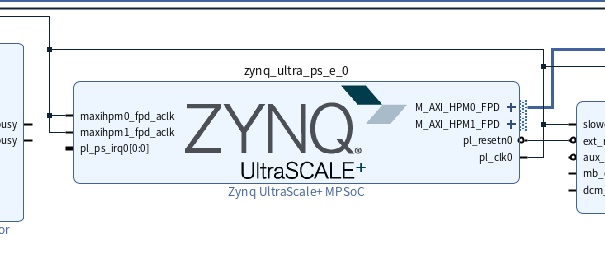

CPUは、Zynqを使用する

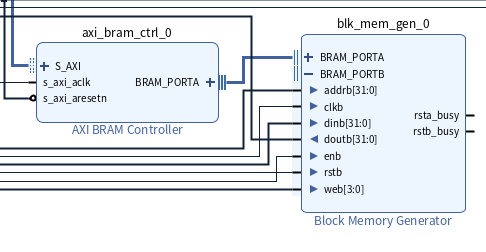

次には、BRAMです。CPUからアクセスするために、AXI BRAM Controllerを使います。

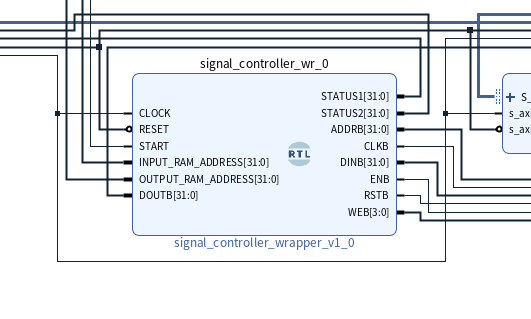

次は、BRAMから画像を読み出して、画像を処理する部分です。Block design上は、signal controller wrapperに含まれています。こちらは自作のモジュールになります。

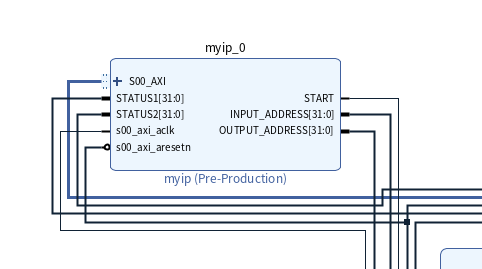

次は、CPUからレジスタアクセスして、画像処理に指示を出すモジュールになります。こちらも自作モジュールになります。

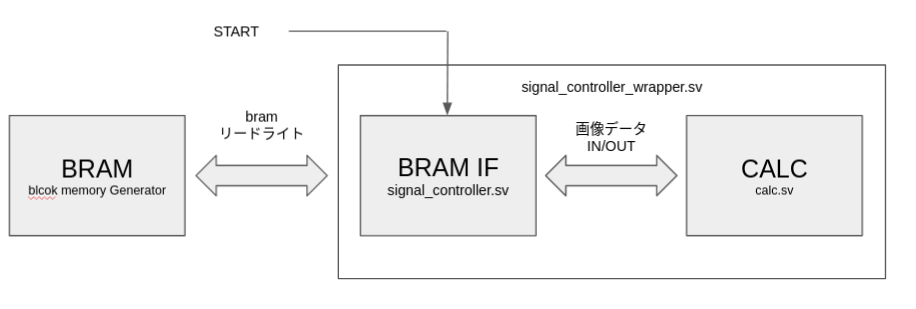

画像処理をするsignal controller wrapperを詳細に見ていきます。

signal controller warpperのブロック図です。

モジュールはこんな感じです。

module signal_controller_wrapper(

//for module control

input CLOCK,

input RESET,

input START,

input [31:0] INPUT_RAM_ADDRESS,

input [31:0] OUTPUT_RAM_ADDRESS,

// output [3:0] STATUS,

output [31:0] STATUS1,

output [31:0] STATUS2,

//BRAM IF

output [31:0] ADDRB,

output CLKB,

output [31:0] DINB,

input [31:0] DOUTB,

output ENB,

output RSTB,

output [3:0] WEB

);各IOの説明です。

- CLOCK 動作クロック

- RESET リセット

- START 信号が1になると、BRAMから画像を読み出します。

- INPUT_RAM_ADDRESS BRAMから読み出すアドレスを指定します。

- OUTPUT_RAM_ADDRESS 画像の加工結果をBRAMに書き出すアドレスを指定します。

- STATUS1,STATUS2 デバック用

- BRAM IF ADDRB CLKB DINB DOUTB ENB RSTB WEB BRAMのポートに接続するIO

signal controllerの中身は、状態遷移をして動作しています。

- READ 状態 BRAMからデータを読み出します。

- CALC状態 画像を加工しています

- WRITE状態 BRAMにデータをライトしています。

- IDLE状態 何もしていない状態

画像処理部分のIOです。

module calc(

input CLOCK,

input RESET,

input INPUT_DATA_ENABLE,

input [31:0] INPUT_DATA[8][8],

output OUTPUT_DATA_ENABLE,

output [31:0] OUTPUT_DATA[8][8]

);今回、このIOに2次元配列を使いたくて、System Verilogで実装をしました。

- CLOCK 動作クロック

- RESET リセット

- INPUT_DATA_ENBLE 1になると、INPUT_DATAのデータを読み出して、計算、画像データの加工を始めます。

- INPUT_DATA 画像データが含まれます。

- OUTPUT_DATA_ENABLE 計算が終了するとOUTPUT_DATA_ENABLEが1になります。

- OUTPUT_DATA 加工された画像データが

今のところ、CALCは、INPUT_DATAをOUTPUT_DATAに入れているだけですが、今後、CALCにDCTの計算を実装する予定です。

今回紹介したモジュールのプロジェクトファイルとソースコードです。

https://github.com/y38y38/myip_start