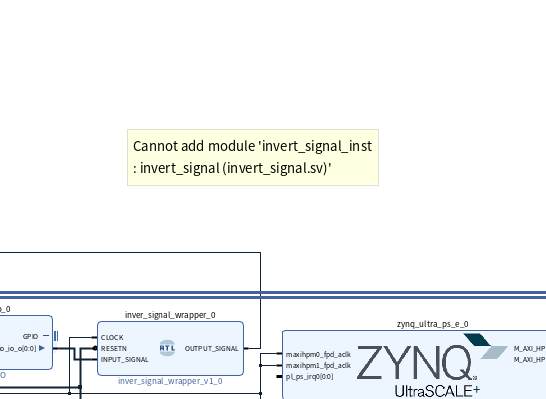

System Verilogで書いたコードを、Vivadoのblock Designに追加しようと思ったら、追加できなかった。

system verilogのファイルは、block desginに追加できないらしい!!

ちょっと工夫したら、間接的に追加できることがわかった。このあたりは独学でやっていると聞く人がいなくて困る。。。

System Verilogのファイルの追加方法

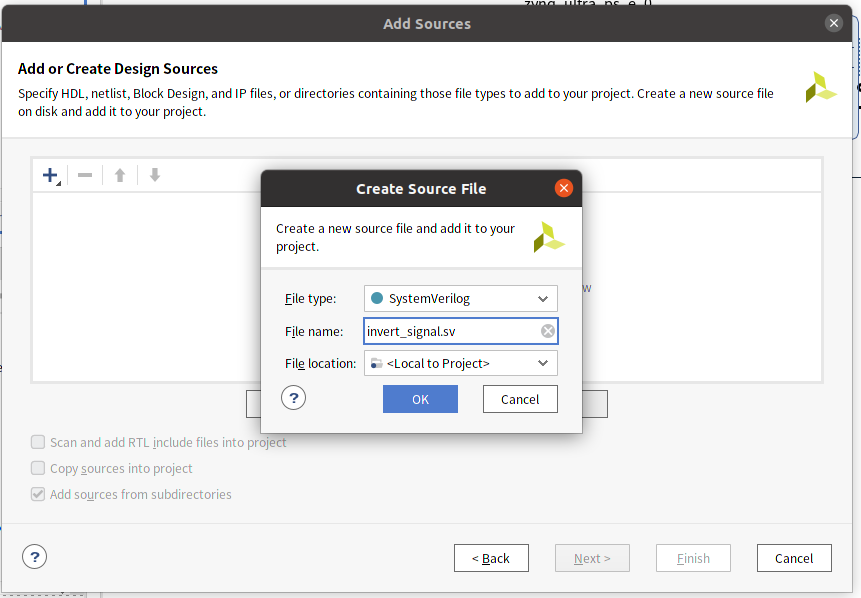

system verilogのファイルを用意する。

コードの中身はこんな感じ。logic とかalways_ffとかsystem verilogの用語を使ってみた。

module invert_signal(

input CLOCK,

input RESETN,

input INPUT_SIGNAL,

output OUTPUT_SIGNAL

);

logic output_signal = 1'b0;

always_ff @( CLOCK ) begin : blockName

if (RESETN==0) begin

output_signal <= 1'b0;

end else begin

output_signal <= ~INPUT_SIGNAL;

end

end

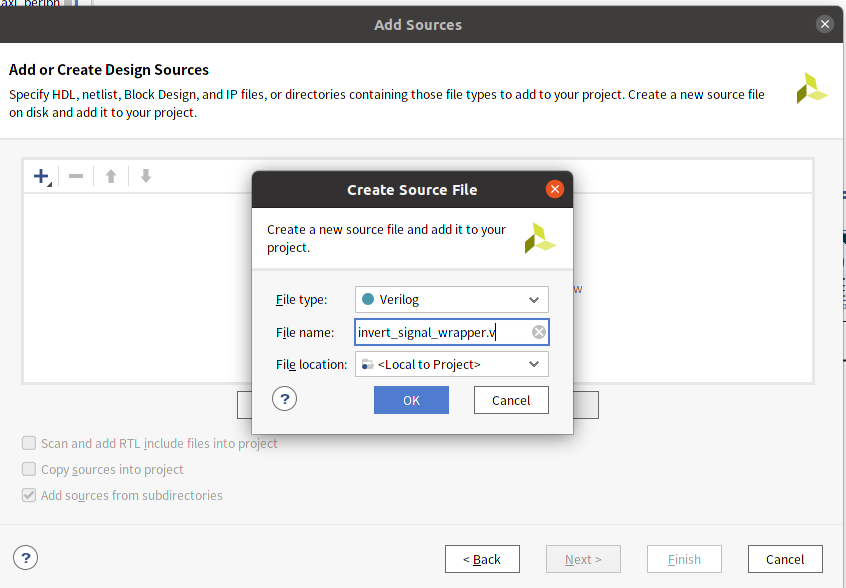

endmoduleこのままだと、block desginに追加できないので、verilogでラッパー用のコードを用意する。

ラッパー用のファイルは、こんな感じ。INとOUTは、system verilogのモジュールと一緒で、system verilog側のコードと接続しているだけ。

module inver_signal_wrapper(

input CLOCK,

input RESETN,

input INPUT_SIGNAL,

output OUTPUT_SIGNAL

);

invert_signal invert_signal_inst(

.CLOCK(CLOCK),

.RESETN(RESETN),

.INPUT_SIGNAL(INPUT_SIGNAL),

.OUTPUT_SIGNAL(OUTPUT_SIGNAL)

);

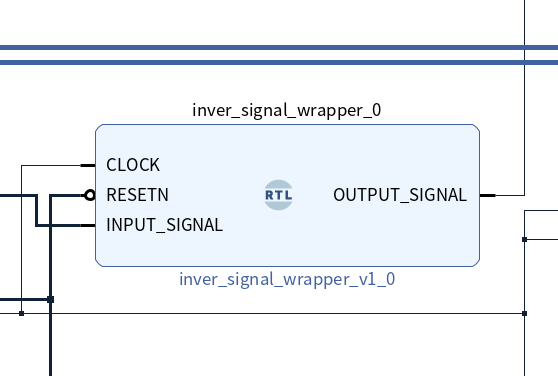

endmoduleこうすると、intert_signal_wrapperは、block desginに追加できるようになる。

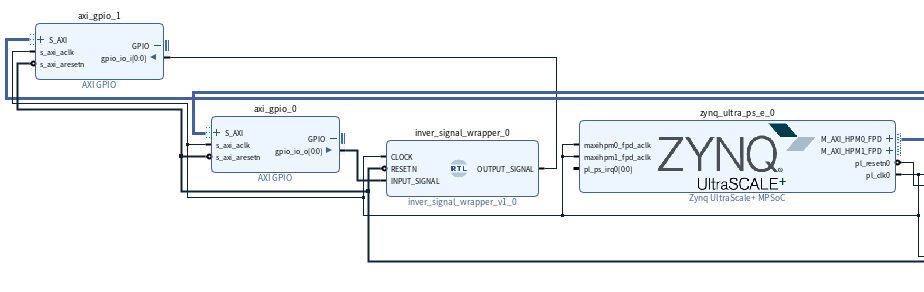

念のため、Generate Bitstreamまで確認しておく。

System Verilogでコードを記載して、Vivadoで使えることがわかった。良かったー。

使用したコードは以下においておく。