AXI Verificationのサンプルを作成した。

以下のサイトを参考にした。

https://marsee101.blog.fc2.com/blog-entry-3781.html

FPGAの部屋のサイトには、VIPの説明が書かれている

https://qiita.com/tethys_seesaa/items/9d4c00212d9ea79b1497

Qiitaのサイトには、VIPのサンプルがあり、参考になったというかコードは利用させてもらった。

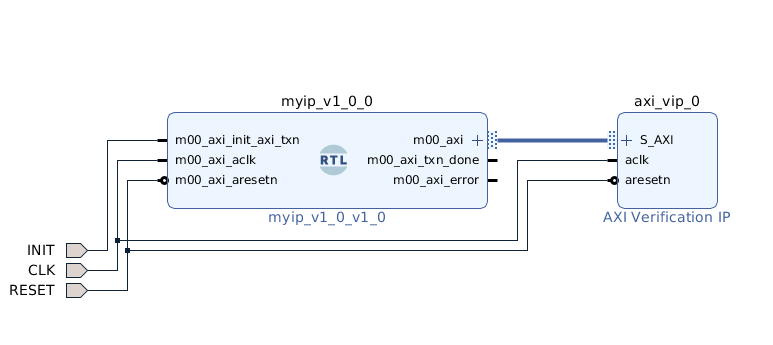

自分は、Master側のIPを作る予定なので、VIP側は、Slave側を用意したかった。サンプルのブロック図を紹介する。

axi_vip_0がAXI Verification IPをSlaveで用意したものだ。myip_v1_0_0は、VivadpのTool→Create And Package New IPで、作ったAXI MaterのIFを持つモジュールだ。

myip_v1_0_0_0は、1回ライトして、1回リードするだけのモジュールで、INITをアクティブすると動き出すようになっている。

そして、次が、作成したシミュレーション用のコードだ。

`timescale 1ns/1ps

import axi_vip_pkg::*;

import design_1_axi_vip_0_0_pkg::*;

module tb();

localparam int LP_CLK_PERI = 16;

localparam int LP_RST_PERI = 64;

// DUT instance

logic INIT, CLK, RESET;

design_1_wrapper dut(.*);

task rst_gen();

RESET = '0;

#(LP_RST_PERI);

RESET = '1;

endtask

task clk_gen();

CLK = '0;

forever #(LP_CLK_PERI/2) CLK = ~CLK;

endtask

task clk_dly(int n);

repeat(n) @(posedge CLK);

endtask

design_1_axi_vip_0_0_slv_mem_t agent;

task init_agent();

agent = new("slave vip mem agent",dut.design_1_i.axi_vip_0.inst.IF); // agent is newed

agent.start_slave(); // agent starts to run

endtask

// Testscenario

initial begin

INIT = 1'b0;

fork

init_agent();

clk_gen();

rst_gen();

join_none

////clk_dly(10);

//wr_tran();

clk_dly(10);

INIT = 1'b1;

clk_dly(1);

INIT = 1'b0;

clk_dly(200);

//rd_tran();

//clk_dly(100);

$finish(2);

end

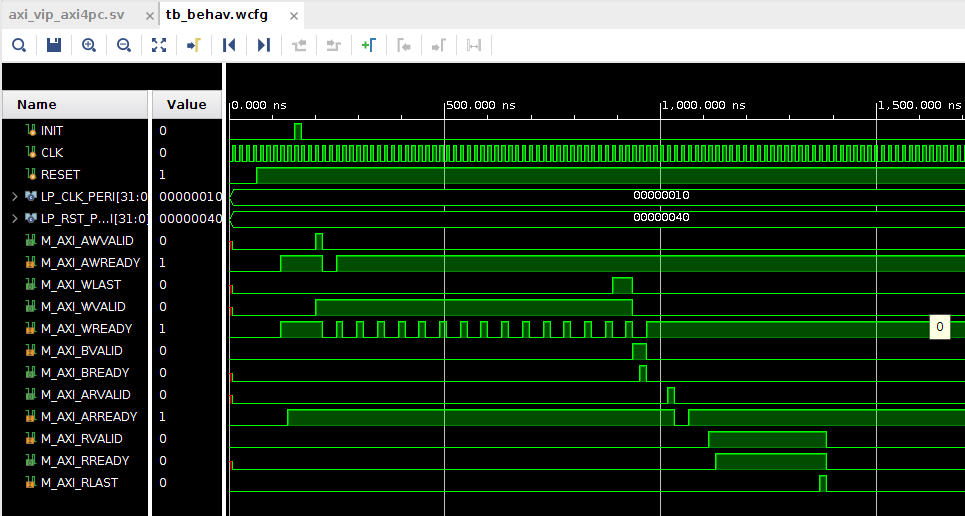

endmoduleこのコードをシミュレーションした結果を以下に示しておく。

作成したコードとプロジェクトは以下においてある。