このFPGAプログラミング大全 Xilinx編のVGA出力の演習をultra96でやってみる。ultra96にVGAの出力はないので、今回はシミュレーションをして、Bitstreamを生成するまでを行った。

いつもどおりチュートリアル1をベースに実装してく。

https://www.element14.com/community/docs/DOC-91053/l/01ultra96vivadointro2018201zip

PS→PLへ出力するpl_clk0は心配なので、pl_clk1で行うことにする。

Open Block Desgin→Diadramで、ZYNQをクリックして、Clock Configuration→Output Clock→Low Power Domain Clocks→PL Fabric Clocksで、PL1を有効にする。本だと、入力周波数は100MHzなので、PL1のクロックを100MHzに合わせる。

そうすると、pl_clk1が現れる

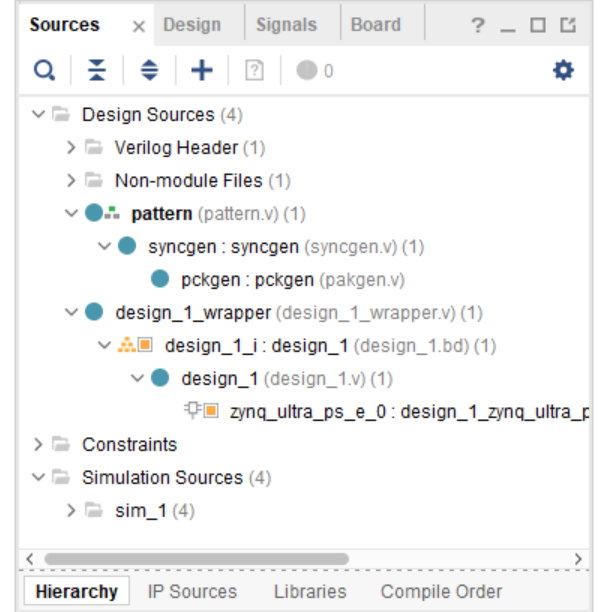

次に、入力したクロックを元に、VGAのHSYNCとVSYNCを生成して、800×600ドットの画面を作る。ファイルは、pattern.v、syncgen.v、pakgen.v、vga_param.vhだ。本の通りの正解のソースコードは、本のサポートページにあるので、それを見ると良いと思う。

コードを追加するBLOCK DESIGN→Source→Design Sources→design_1を右クリックして、Add Sourcesを選択 Add design Sourcesで、4個のファイルを追加する。

また、BLOCK DESIGN→Source→Design Sources→design_1を右クリックして、Create HDL Wrapperをする。

(ZYNQのpl_clk0とmaxihpm0_fpd_aclk,maxihpm1_fpd_aclkを接続しておく)

Create HDL Wrapperした順番とか、Add Sourceした順番で、たぶんTopがpatternになったり、design_1_wrapperになったりする。気持ち悪いので、design_1wrapperを右クリックして、Set as Topでtopにしておく。

(今日時点でtopの意味はしらないが重要な定義だと思う。)

次に、patternをZYNQと接続するBLOCK DESIGNで、patternをドラック&ドロップして、Diagramに置く。

次に、追加したpattern_0とZYNQを接続する。pl_clk1とCLK、pl_resetn0とRSTを接続する。

次に、pattern_0を外部端子と接続する。各端子で、右クリックをしてMake Externalを選択する。

全部外部接続したらこんな図になる

ちなみに、Validate designすると、RSTとCLKが同期していないとwarningがでるが気にしない。

次は、制約ファイルを作成する。Run Synthesisを実行する。実行したらOpen Synthesized Design→Schematicを選択して回路を確認する。

図を見てでもいいし、I/O Portsをクリックしてでもいいし端子名を確認して、制約ファイルを作成する。

次に、ultra96の回路図を確認する。VGAをもし接続するなら、LS EXPだと思うので、適当に線を選択する。HD_GPIO_0~HD_GPIO_13までを使用することにする。

で、このHD_GPIO_0等は、回路図を見て、BANK26に接続していることがわかる。HD_GPIO_0を見ると、ZYNQのD7に接続していることがわかる。これを1本ずつ制約ファイルに反映させる。

制約ファイルはこんな感じになる。

b.xdc————–

set_property PACKAGE_PIN D7 [get_ports {VGA_B_0[0]}]; #HD_GPIO_0

set_property PACKAGE_PIN F8 [get_ports {VGA_B_0[1]}]; #HD_GPIO_1

……

set_property IOSTANDARD LVCMOS18 [get_ports -of_objects [get_iobanks 26]]

——————–

作成した制約ファイルをBLOCK DESIGN→Source→Design Sources→Constraintsで右クリックして、Add Sourceして追加する。そして、Generate Bitstreamを実行する。

で、bistreamができた!

で、今回は、VGAのアダプタを買うのはなんなんで、シミュレーションで確認する。趣味レーションとしては、pattern_test.vというシミュレーションのコードを追加する。BLOCK DESIGN→Source→Simulation Sourcesから右クリックして、Add Sourcesを選択して追加する。で、ここでもシミュレーションするときに、topを選択する必要がある。今回はpattern_test.vでシミュレーションしたいので、patern_testで右クリックしてset as topを選択する。

たぶんだけど、desig_1_wrapperは、ZYNQのPSをシミュレーションしてくれるのではないかなぁと思う。

では、シミュレーションをする。SIMULATION→Run Simulation→をクリックする。今回は、Run Behaviorval Simulationを選択する。そして、再生ボタンを3回ほど押す。(なぜか最初の2回はすぐ終わる。。。意味不明。。。)

シミュレーションが終わると、最初はUntitled 1みたいな名前のWav画面が表示される。見たい信号を登録していないと何も表示されていないはずだと思う。

信号の登録方法は、Scopeでファイルを選択すると、そのファイルの信号が、Objectsに表れて、その中で、見たい信号を右クリックして、Add to Wave WindowするとWavの監視対象になる。

シミュレーションの結果だ。なんとなくいい感じになってそうー。

本はZYBO向けに作られたコードだからどうかわからないけど、うまくいかなかったので、少し変更した部分について説明する。

今回、MMCME2を使ったが、本と使用が違った。Vivadoのバージョンも違うしそんなものだろう。以下のような変更した。VCOの範囲が少し変わったみたい。

MMCME2_BASE #(

….

.CLKFBOUT_MULT_F(25.0), // 乗数M(2.000-64.000)

….

.CLKIN1_PERIOD(0.1), // CLKINの周期

….

.CLKOUT0_DIVIDE_F(50.0), // 除数Q(1.000-128.000)

….

.DIVCLK_DIVIDE(2), // 除数D(1-106)

….

)

[DRC PDRC-179] MMCM_adv_ClkFrequency_div_no_dclk: The computed value 625.000 MHz (CLKIN1_PERIOD, net pl_clk1) for the VCO operating frequency of the MMCM site MMCM_X0Y1 (cell design_1_i/pattern_0/inst/syncgen/pckgen/MMCME2_BASE_inst) falls outside the operating range of the MMCM VCO frequency for this device (800.000 – 1600.000 MHz).

設計したコード、プロジェクトはこちらに置いてありますー。