前回は、GPIOのIPを使用した。今回は、独自のIPを使用して、Lチカを実行してみようと思う。しかし、今のところ、ultra96のPLには、外部からクロック入力がされていないと思う。。そのため、PSからPLに入力されているクロックを使用することになる。

基本は、ultra96のチュートリアル1をベースに作成していく。差分だけここで示していく。

https://www.element14.com/community/docs/DOC-91053/l/01ultra96vivadointro2018201zip

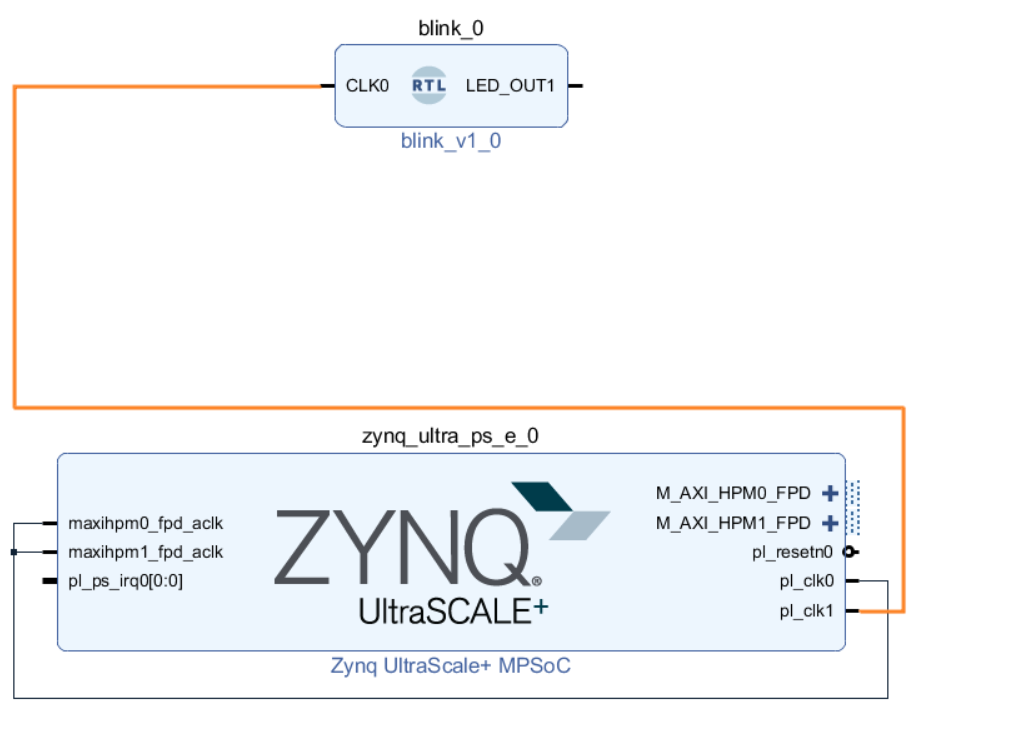

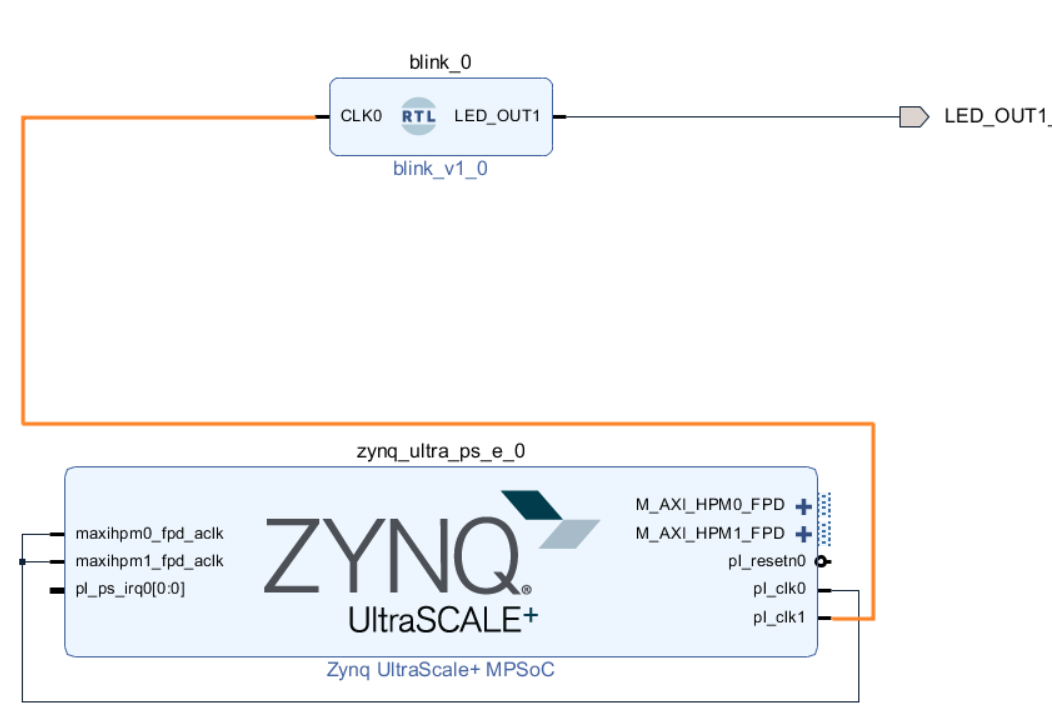

チュートリアル1でもpl_clk0がでてくるが、今回はpl_clk1を使用する。

Create Block Designで、ZYNQを追加して、Run Block Automationして、チュートリアル1にあるように、maxihpm0_fpd_aclkとpl_clk0、maxihpm1_fpd_aclkとpl_clk0をつなぐ。

pl_clk1の設定

このpl_clk0を調べてみる。BLOCKDESIGN→DiagramからZYNQをダブルクリックする。Clock Configuration→Output Clocks→Low Power Domain Clocks → PL Fabric Clockが、PS→PLへのクロックのようだ。

デフォルトだと、PL0だけチェックが入っていない。チェックを入れると、他のClockも使用することができそうだ。今回は、pl_clk1を使用するので、PL1にチェックを入れる。

本当は、pl_clk0で回路をつくろうと思ったのだが、GenerateBitStreamでエラーになったので、pl_clk1でする。

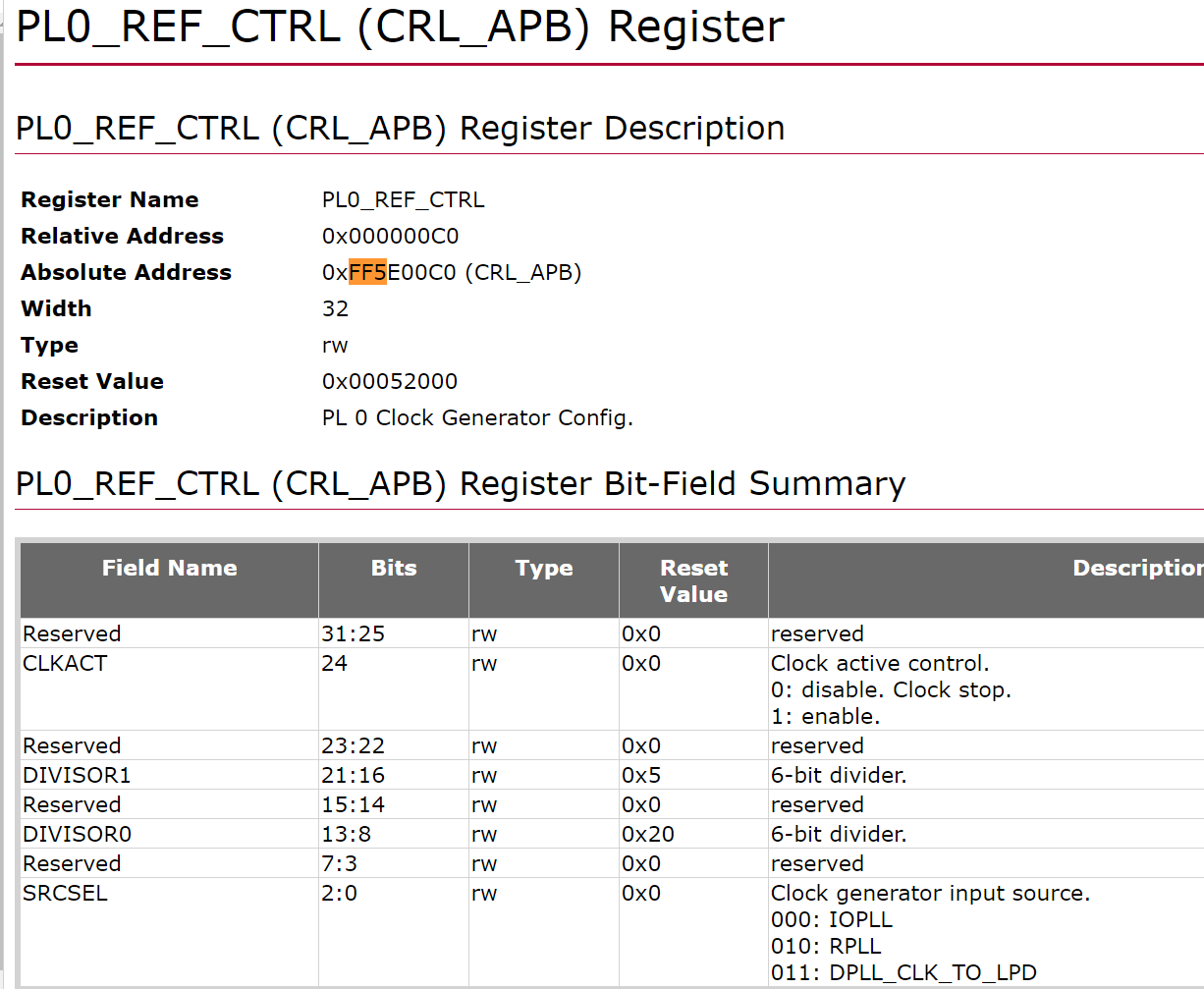

ちなみに、これらの設定は、ZYNQのレジスタマップで、確認できる。たぶんだけど、Vivado側では初期値の設定ができて、あとで、PSが起動後に、CPUで書き換えることができると思う。(手順はいろいろ必要だと思うけど)

https://www.xilinx.com/html_docs/registers/ug1087/ug1087-zynq-ultrascale-registers.html

のレジスタマップの、0xFF5E00C0が、PL0のクロックの設定箇所になる。

Lチカのロジックを追加

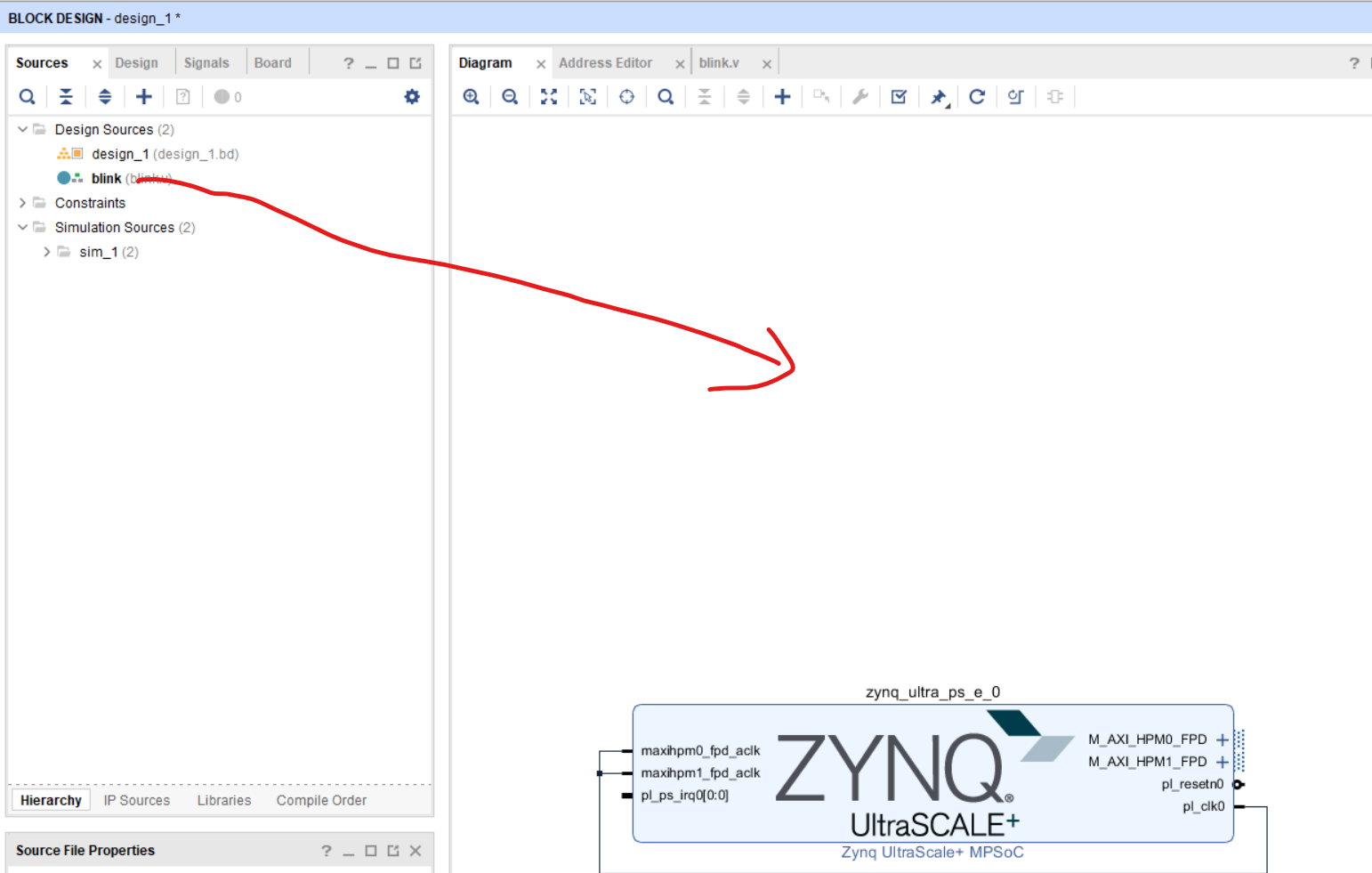

Lチカのロジックを追加する。以下の記載をblink.vとして保存しておく。

———————-ここから

module blink(

input CLK0,

output LED_OUT1

);

parameter CNT_10SEC = 27’d999999999; // 100MHz clk for 1sec

reg [26:0] cnt = 27’d0;

reg onoff = 1’d1;

always @(posedge CLK0) begin

if (cnt == CNT_10SEC) begin

cnt <= 27’d0;

onoff <= ~onoff;

end

else begin

cnt <= cnt + 27’d1;

end

end

assign LED_OUT1 = onoff;

endmodule

結果、以下のように、RTLが配置される。

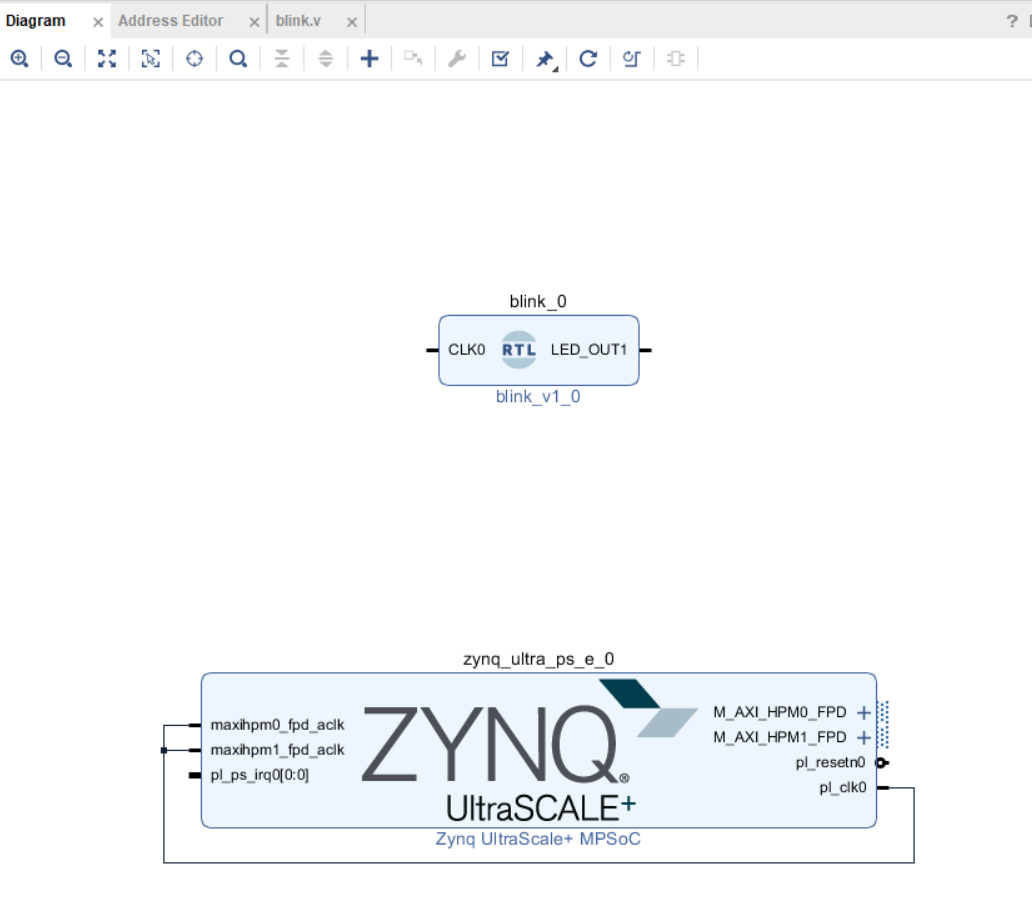

クロックの接続

次に、マウスを使って、pl_clk1とCLK0を接続する。

次に、blinkから外部の端子に接続することを定義する。LED_OUT1で、右クリックして、Mark Externalを選択する。そうするとLED_OUT1_0が現れる。

制約ファイルの作成

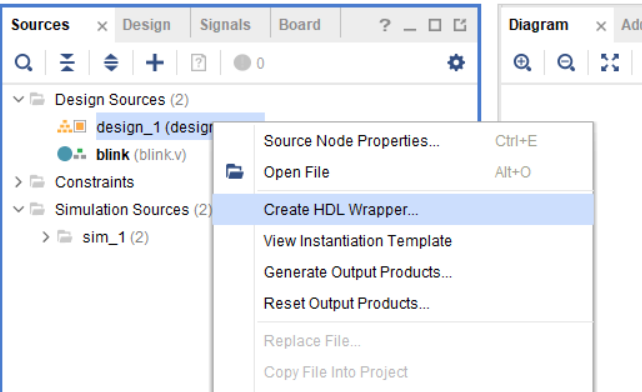

回路は一通り組めたので、BLOCK DESIGN→Sources→Design Sources→design_1で、右クリックで、Create HDL Wrapperを選択する。

次に、LED_OUT1_0を、外部のどのPINに配置するかを記載する制約ファイルを作成する。前回調べたように、ultra96だと、A9に外部のLEDが接続されている。

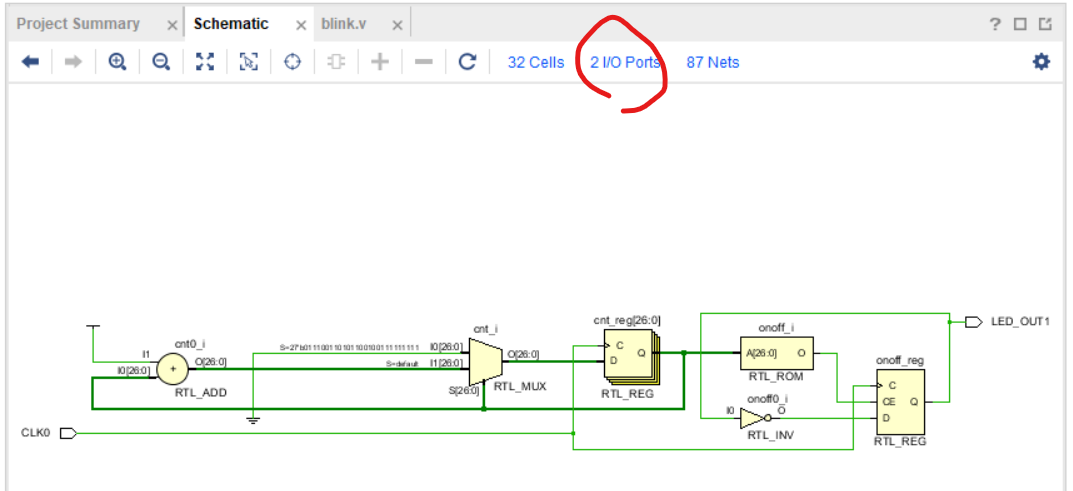

最初に、LED_OUT1_0の端子名を調べる。Flow Navigator→RTL ANALYSIS→Open Elaborated Designを実行する。

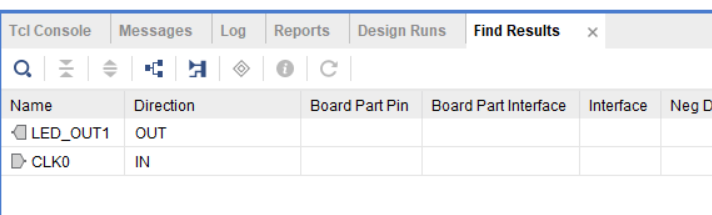

回路図がでてきたら2 I/O Portsをクリックして、端子名を確認する LED_OUT1がポート名っぽい。

と思ったが、端子名は違うっぽいLED_OUT1_0を指定する。よくわからないが、後ででGenerate BitStreamでエラーになった。

制約ファイルの中身になります。この記載を.xdcの拡張子で保存する。

—————-ここから

set_property PACKAGE_PIN A9 [get_ports {LED_OUT1 _0 }]; # “E8.CSI0_MCLK”

set_property IOSTANDARD LVCMOS18 [get_ports -of_objects [get_iobanks 26]]

ここまで———————-

Flow Navigator→Open Block Design→BLOCK DESIGN→Sources→Constraintsから右クリックをして、Add Sourcesから保存した制約ファイルを追加する。

Bitstreamの作成

Flow NavigatorからGenerate Bitstreamをクリックする。で、できたらExport→Export Hardwareで、include BitStreamをチェックして、exportする。

ソフト

ソフトウェアが側は、チュートリアル2と同じでOK.できたら、Program Bitstreamして、helloworldを実行する。

https://www.element14.com/community/docs/DOC-91052/l/02ultra96vivadohelloworld2018201zip

で、うまくいっていれば、USBの右側の小さいオレンジのLEDが5秒ぐらいでチカチカしているはずだ!!

ps_clk0だとエラーだったり、制約ファイルへ記載する端子名だったり、vivadoの使い方だったり、ぜんぜんわからないけど。。。なんとかなった。って。。。。結構時間を費やしましたー。