ultra96に搭載されているZynqにはARMが2個のっている。しかし、基板上にはUARTは1個しかない。そうだとすると、デバックの場合は、どちらかのCPUの出力だけを観測することになる。

それだと、のちのちARMを2個使ったデバックをする場合に困るので、Low Speed のコネクタからUARTを出すようにしようと思う。

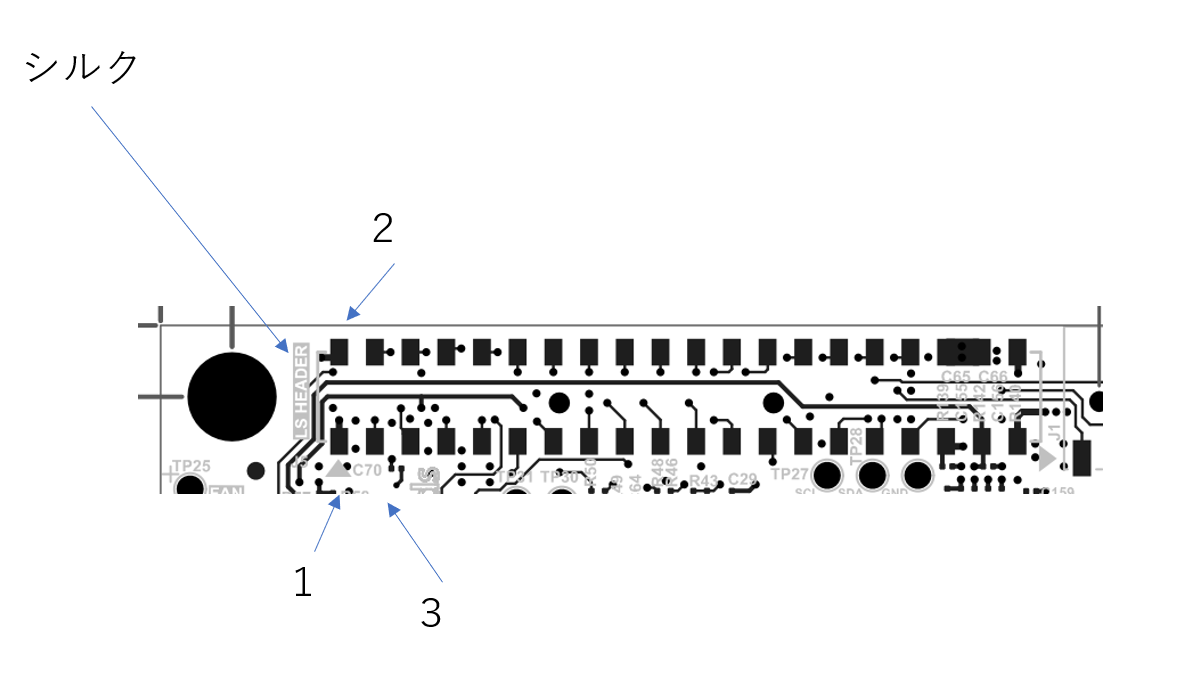

これが、Low Speedのコネクタだ。ここに、UARTを接続しようと思う。

最初に、Low Speed コネクタの回路を確認する。回路を見ると、Low Speed コネクタに接続されたMIOはそんなに多くなかった。またUARTののRx/Txは連番でとらないといけないようで、候補は

a)MIO36_PS_GPIO1_0、MIO_37_PS_GPIO1_1

b)MIO42_PS_GPIO1_0、MIO_43_PS_GPIO1_1

のどちらかになる。

ちなみに、MIOはPSに接続される端子で、HD_XXXはPLに接続する端子だと思う。

PLにUARTのロジックを配置することができるとほぼどこの配線でもOKになるが、今の自分にはそんな知識はないので、PSに接続できるMIOから選択する。

なので、今回はb)にUARTを接続する。

以下、LS(Low Speed)のコネクタの回路図だ。

回路図のリンク

で、物理的には、図面を見ると、勝手に、シルクがついている方が、先頭側になると思ったので、1、2、3…とPINの配置になっていると想像した。(結果はあっていた)

図面のリンク

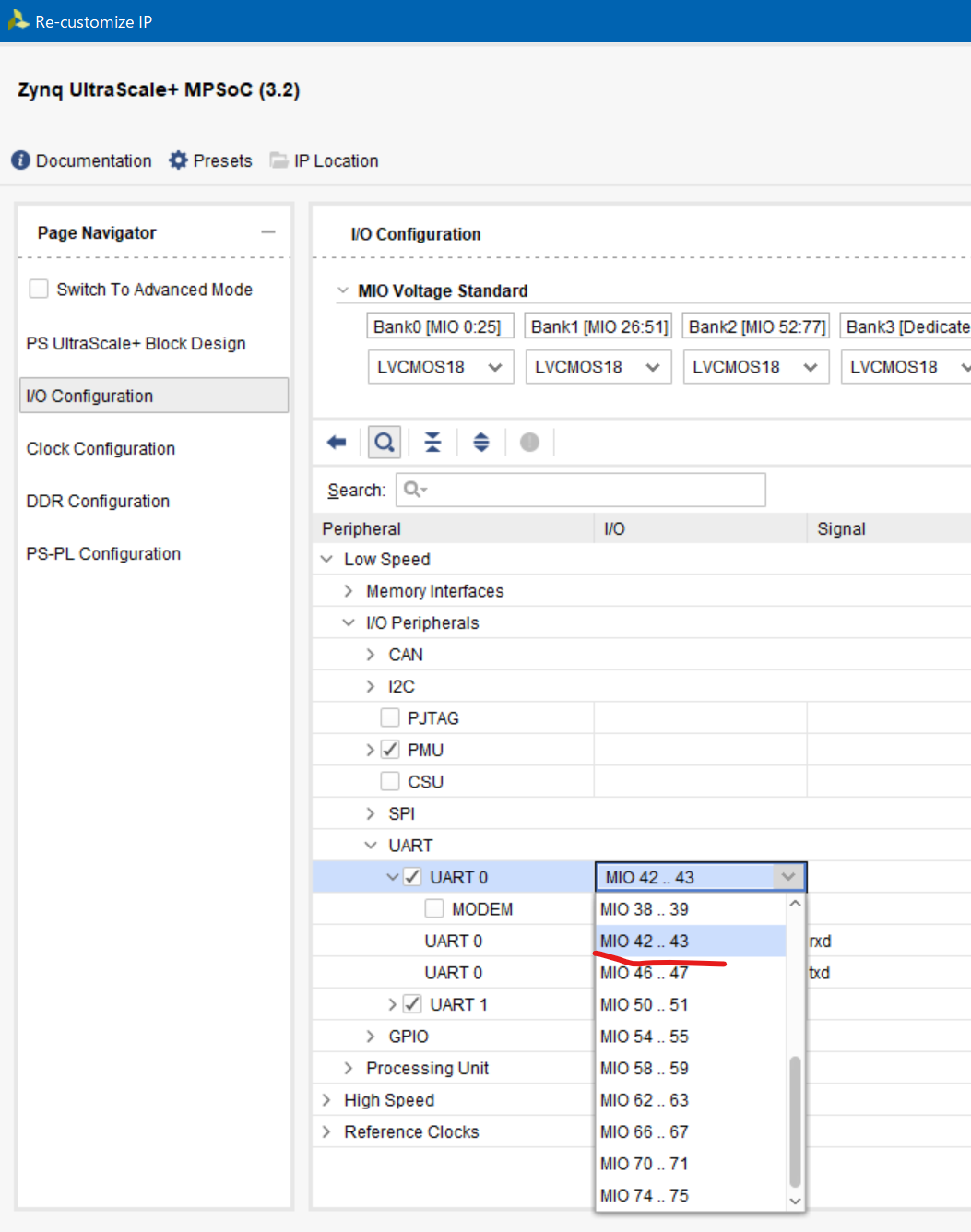

では、Zynqの設定をしていく、参照にしたのは、チュートリアル01を参考にした。

Create Block Designをした時に、ZYNQ UltraSCALE+をダブルクリックする。Re-customaize IPの画面で、左のI/O Configurationを選択してLowSpeed→UART→UART0を選択して、I/Oで、MIO42..43を選択する。

そして、チュートリアル01のように、HDFファイルを生成して、Generate BitStreamして、Export Hardwareをして、チュートリアル01を終了する。

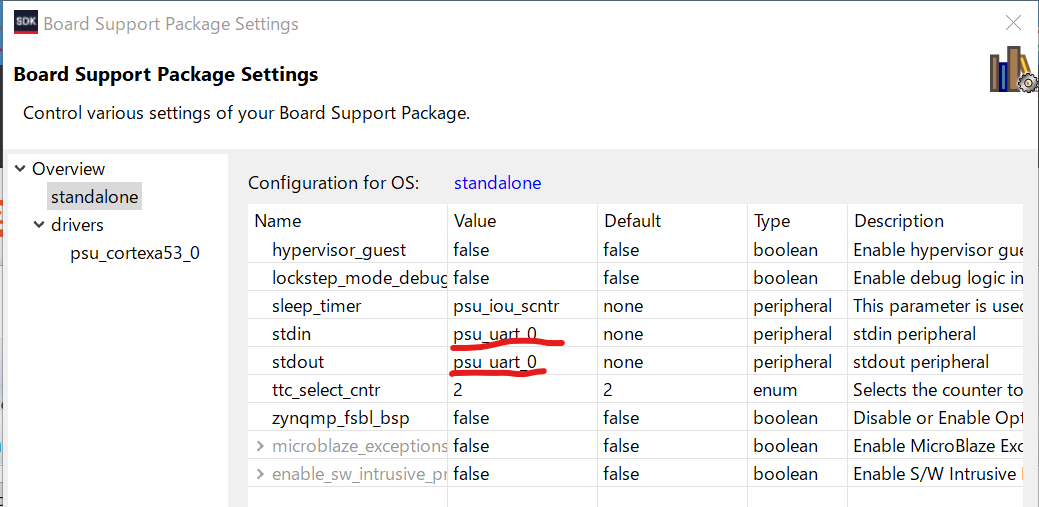

で、その結果をもとに、チュートリアル02を実行する。

チュートリアル02では、stdinとstdoutをUART1を選択するようになっているけど、今回は、UART0を接続したので、UART0を選択する。

これで、ZYNQ側の設定はできたので、物理的な確認をしていく。

今回は、UARTの接続は、以下のデバイスを購入した。

DSD TECHのSH-U09C5

ultra96側のLowSpeedコネクタはメス、購入したデバイスはオスだったので、オス-メスのケーブルをamazonで購入した。

で、ultra96のLow SpeedのPINの10、14番に刺した。

・ultra96の10番PINに、SH-U09C5のTXD

・ultra96の14番PINに、SH-U09C5のRXD

を接続する。

ultra96側はこんな感じで、

SH-U09C5側はこんな感じである。

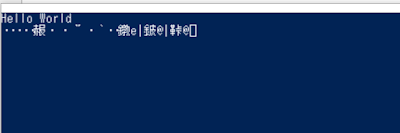

で、チュートリアル02のHello Worldを実行すると、新規に追加したUART0側に、「Hello World」が表示された。

実行したファイル類はこちらです。

https://github.com/y38y38/fpga/tree/master/ultra96_uart_add

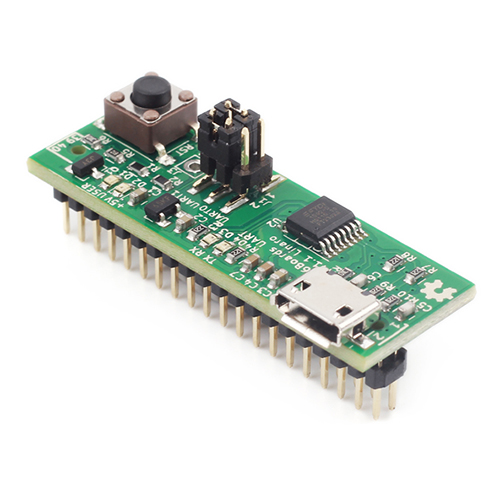

しかし、実は、LowSpeed用の基板は、96Boardsで売っていて、そちらの基板を買うと簡単にできた。。。以下は、売っている基板だ。

ここで売っている

初めて、ケーブルとか買って、ドキドキしながらやったので、簡単なことだけど面白かった!